FPGA-based Motor Control

As a result of the technological progress in the field of integrated circuits the density of logic functions on a chip has increased enormously, whereas the cost of reprogrammable logic has reduced drastically. Hence, FPGAs (Field Programmable Gate Areas) become more and more attractive in the field of drive controls. Furthermore FPGAs provide several advantages compared to state of the art processor-based controls, namely:

- True parallel processing

- Fast processing (in the range of nanoseconds)

- Typical computational delay of 100 ns

- Greater flexibility from the logic complexity and development point of view

- The bit width can be specified individually for each signal, thus the required numeric accuracy can be achieved by an appropriate design

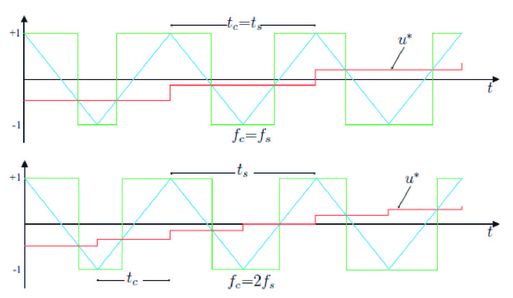

Traditionally, the inner current control loop of a cascaded AC-motor control structure (e.g. Field Oriented Control) is realized on a DSP or microcontroller (µC) utilizing the well-known regular sampling technique. In regular sampling the acquisition of measured data and the controller execution is synchronized with the triangular pulse width modulation (PWM) carrier. Thus, the controller sampling frequency fC can be same or twice the PWM frequency fs as shown in Figure 1.

The sequential execution of the control algorithm on processor-based controls implies a total dead time TΣ of 1.5*TC (due to the computational delay of one sampling step TC and additional delay of 0.5*TC caused by the data acquisition mechanism). This additional delay has to be considered in the controller design and is typically approximated using a first order lag element with the time delay TΣ. It can be shown that the bandwidth of the closed loop transfer function of the system is inversely proportional to the dead time TΣ. For standard drives the achievable bandwidth of processor-based controls may be sufficient, but for high performance servo drives it is just insufficient. The poor achievable bandwidth directly results in low dynamics. This problem can be overcome by reducing the total dead time of the closed loop transfer function.

Before microcontrollers came up the control realization was based on analog circuits. Such an analog realization does not introduce any dead time in the system, so that the achievable bandwidth is quite high, theoretically even infinite. However the analog realization has its own drawbacks, which are offset, nonlinearity, drift, nonchangeable control parameters, etc. Therefore the goal is to achieve the same performance in the digital domain but avoiding these drawbacks.

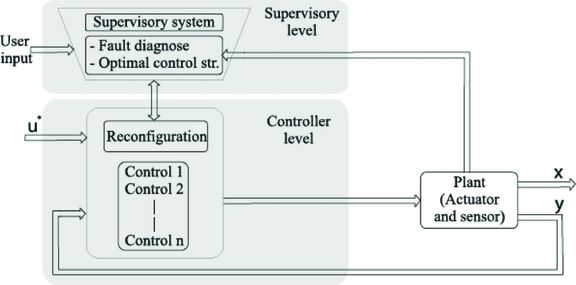

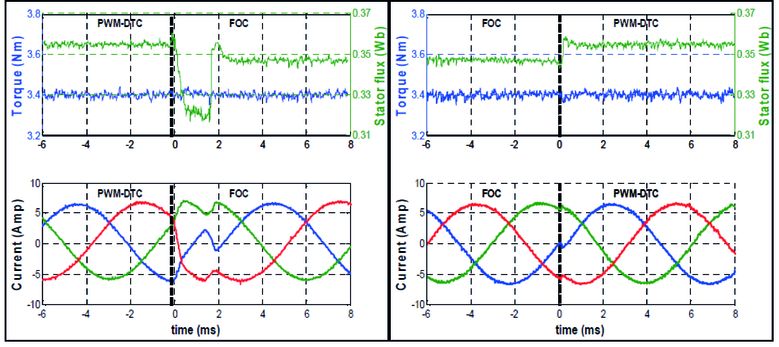

A control realization based on FPGA currently seems to be the best approach to achieve a performance that is very close to analog controls on a digital platform. The resulting controls can be referred to as quasi-continuous control realizations. The possibility of parallel execution also enables the handling and implementation of multiple/ complex control schemes on a single control platform. Thus, it is possible to realize a dynamically reconfigurable control structure as shown in Figure 2. The relevant trajectories during transition between a FOC and DTC control structure on a testbench are depicted in Figure 3.

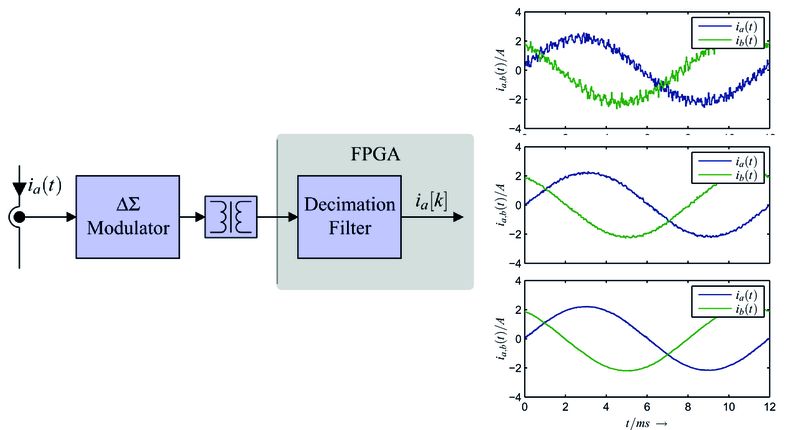

The concept of reconfigurable control is expected to achieve a control performance close to the respective optimum in the entire operation area while providing a certain degree of fault tolerance with respect to sensor failures. In addition to the technical goals, the research work is also focused on the general understanding and methodology of reconfigurable control systems and the usage of FPGAs in the domain of electrical drives control. Also, efficient realizations of data acquisition mechanisms based on Δ∑-ADC are investigated. The advantages of Δ∑-ADCs lie in the possibility to scale the resolution at the cost of computation time and the ease to incorporate galvanic isolation. In Figure 4, the structure of the mentioned Δ∑-ADC is shown along with some measured current signals which are gained at different decimation rates D.

References:

| [1] | S. Mathapati FPGA-Based High Performance AC Drive Universität Paderborn, Germany, 2011 |

| [2] | S. Mathapati, J. Böcker Dynamically Reconfigurable Control Structure for Induction Motor Drives on FPGA Control Platform EPE Journal, Vol. 20-1, 2010 |

| [3] | C. Paiz, J. Hagemeyer, C. Pohl, M. Porrmann, U. Rückert, B. Schulz, W. Peters, J. Böcker FPGA-based realization of self-optimizing drive-controllers 35th Annual Conference of IEEE, Industrial Electronics, 2009 (IECON) vol., no., pp.2848-2853, 3-5 Nov. 2009, Porto, Portugal |

| [4] | W. Peters, B. Schulz, S. Mathapati, J. Böcker Regular-Sampled Current Measurement in AC Drives Using Delta-Sigma Modulators 13th European Conference on Power Electronics and Applications (EPE2009), Barcelona, Spain, 2009 |

| [5] | B. Schulz, C. Paiz, J. Hagemeyer, S. Mathapati, M. Porrmann, J. Böcker Run-Time Reconfiguration of FPGA-Based Drive Controllers 12th European Power Electronics and Adjustable Speed Drives Conference, Aalborg, Denmark, 2007 |