Studierender: Rohan Narkhede

Betreuer: Rüdiger Ibers

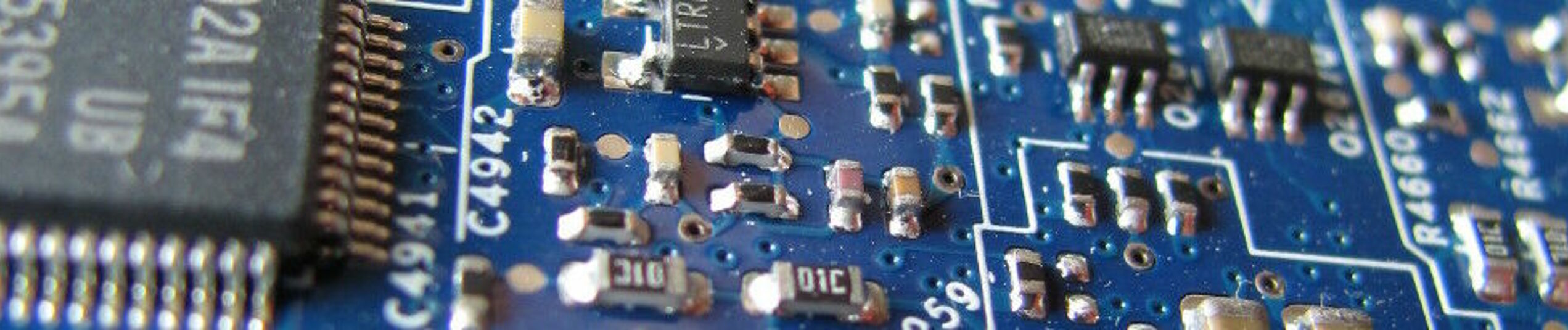

Auch ein fehlerfreier Entwurf und die Verifikation eines Schaltungsdesigns können nicht sicherstellen, dass eine produzierte Schaltung hinterher auch wirklich funktioniert. Fehler treten auch während der Produktion auf, z.B. durch Staubkörner, welche Kurzschlüsse verursachen oder falsch ausgerichtete Masken. Nicht alle diese Fehler sind nach der Produktion direkt sicher und können mit entsprechenden Tests detektiert werden. Verengte Leitungen oder Isolationen müssen z.B. durch ein Burn-In zum Durchbruch gebracht werden, bevor die Fehler erkennbar werden. Da immer kleinere Schaltungsstrukturen ein effektives Burn-In erschweren, können fehlertolerante Schaltungen als alternative Betrachtet werden. Sie können aber nicht nur manche Produktionsfehler kompensieren, sondern auch Schaltungsalterung bis zu einem gewissen Grad erkennen und kompensieren.

Das Ziel der Arbeit ist es, in VHDL eine Arithmetisch Logische Einheit (ALU) für einen Prozessor zu entwickeln, welche in der Lage ist, durch Zeitliche-, Algorithmische-, oder Hardware-Redundanz Fehler zu tolerieren, ohne dabei die Schaltung übermäßig zu vergrößern.

Voraussetzungen:

- Kenntnisse in VHDL

- Kenntnisse in C++