VLSI Testing

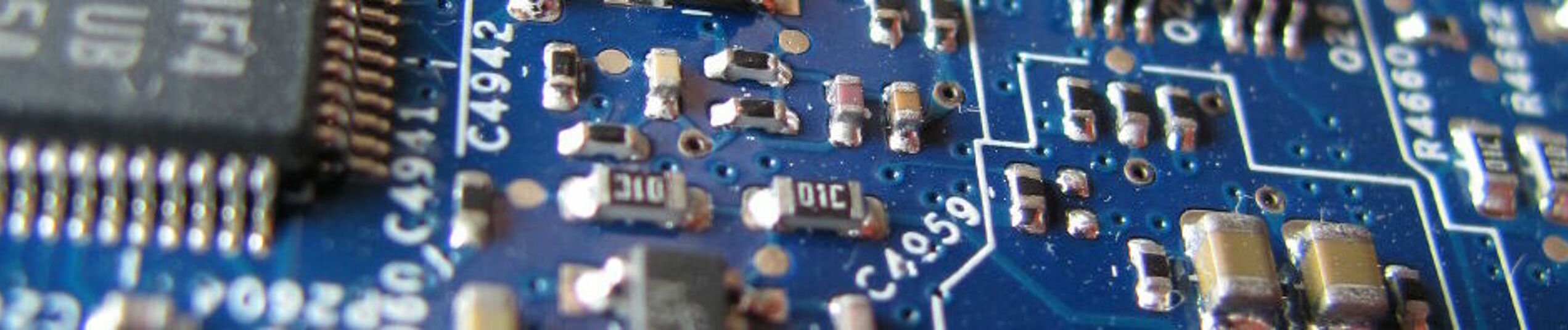

Description

The course "VLSI Testing" focuses on techniques for detecting hardware defects in micro-electronic circuits. Algorithms for test data generation and test response evaluation as well as hardware structures for design for test (DFT) and on-chip test implementation (BIST) are presented.

Content

- Fault models

- Testability measures and design for test (DFT)

- Logic and fault simulation

- Automatic test pattern generation (ATPG)

- Built-in self-test (BIST), in particular test data compression and test response compaction

- Memory test

- ...

Literature

- Michael L. Bushnell, Vishwani D. Agrawal: „Essentials of Electronic Testing for Digital, Memory, and Mixed-Signal VLSI Circuits“, Boston, Dordrecht, London: Kluwer Academic Publishers, 2000

- Laung-Terng Wang, Cheng-Wen Wu, Xiaoqing Wen: „VLSI Test Principles and Architectures: Design for Testability“, Morgan Kaufmann Series in Systems on Silicon, ISBN: 0123705975

Exam

oral exam, appointment upon agreement

Requirements

Lecture notes

More detailed information for students can be found directly in the panda course.

Module group

Computer Engineering (Master):

- Compulsory elective module: VLSI Testing

- Specialization: Embedded Systems, Nano/Microelectronics

Elektrotechnik (Master):

- Mikroelektronik

Informatik (Master):

- Compulsory elective module: VLSI Testing

Electrical Systems Engineering (Master):

- Electronics and Devices

back to course list