Leistungselektronik und Elektrische Antriebstechnik Prof. Dr.-Ing. Joachim Böcker

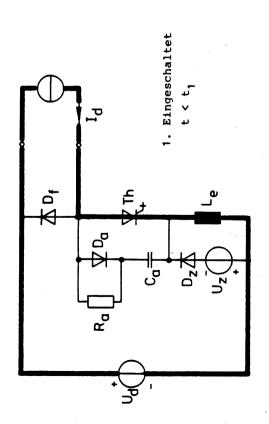

# Lehrveranstaltung:

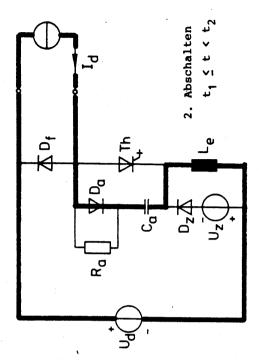

# Bauelemente der Leistungselektronik

Dozent: Dr.-Ing. N. Fröhleke

Stand: April 2005

## **Einleitung**

Verteilung Energie In der Erzeugung, und Nutzung elektrischer erlangen leistungselektronische Umformungen klassischen neben den Methoden mittels immer größere Bedeutung. Weltweit sind heute 40% des gesamten Transformatoren Energiebedarfs auf die Nutzung der elektrischen Energie zurückzuführen, Tendenz steigend. Schätzungen gehen davon aus, dass in einigen Jahren ca. 80% der in Deutschland erzeugten Energie über eine oder mehrere leistungselektronischen Stufen auf dem Weg vom Erzeuger zum Verbraucher umgeformt und gestellt werden.

Die herausragenden Eigenschaften elektrischer Antriebe im Vergleich zu pneumatischen und hydraulischen Antriebssystemen liegen im hervorragenden Wirkungsgrad und in der sehr direkten, hochdynamischen Umsetzung von Information in Aktion. In dieser Wirkkette spielt wieder das leistungselektronische Stellglied durch seine einfache informationstechnische Ansteuerbarkeit und die geringen Verluste eine entscheidende Rolle. Die anhaltende Diskussion über Energieeffizienz und die zunehmende Bedeutung der Erschließung regenerativer Energien hat die Möglichkeiten/Notwendigkeiten des Einsatzes und die Vorteile der Leistungselektronik sogar in die Öffentlichkeit und Politik getragen, was sich in entsprechenden Forschungsförderprogrammen niederschlägt. Denn leistungselektronische Umformer treffen wir bisher vornehmlich im Bereich kleiner und mittlerer Leistungen (einige Watt ... einige zehn MW) an, seltener aber im Bereich von 100 MW und darüber. Zusätzlich gibt es nicht nur in der Automobiltechnik sonder auch in der Luftfahrt das Bestreben, Druckluft und Hydrauliksysteme zu ersetzen oder zu minimieren aus den o.g. Gründen in Verbindung mit den Forderungen nach Servicekostenreduktion, Nichtbrennbarkeit und höherer Verfügbarkeit.

Eine leistungselektronische Schaltung wird im Vergleich zur Elektronik und Mikroelektronik nur von einer mittleren Zahl von Bauteilen wie Schalter, Spulen und Kondensatoren oder Transformatoren gebildet. Als idealer Schalter wird ein verlustloses Ventil bezeichnet, dass im eingeschalteten Zustand keine Durchlassspannung und im ausgeschalteten Zustand keinen Sperrstrom aufweist und Schaltvorgänge, die ohne Verzögerung unendlich kurz verlaufen. Für die Schaltvorgänge benötigt der ideale Schalter keine Ansteuerleistung. Er ist beliebig sperrspannungsfest und kann jeden Strom führen.

Analog gilt für die idealen Reaktanzen, dass eine ideale Spule nur ein magnetisches Feld und ein idealer Kondensator nur ein elektrisches Feld speichert, ohne Verluste zu generieren.

In der Realität verhalten sich leistungselektronische Bauelemente abweichend von den geschilderten idealen Merkmalen, aber die Fortschritte im Bereich der Bauteiltechnologien lassen sie den idealen Eigenschaften merklich annähern. Ziel dieser Veranstaltung ist, durch ein tiefer gehendes Verständnis in Bauteilfragen soll die optimierte Anwendung der Komponenten ermöglicht und eine vorausschauende Sensibilität für vorteilhafte Neuentwicklungen geschaffen werden. Weil aber nicht nur die Leistungshalbleiter Bauelemente wie zuvor genannt eine leistungselektronische Schaltung bilden, sondern neben den passiven Bauelementen auch noch Ansteuer- und Entlastungsschaltungen dazu gehören, wurde die physikalische Behandlungstiefe bei den Halbleitern eingeschränkt. Andernfalls würde die Stofffülle ausufern.

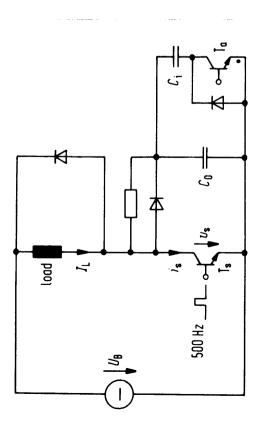

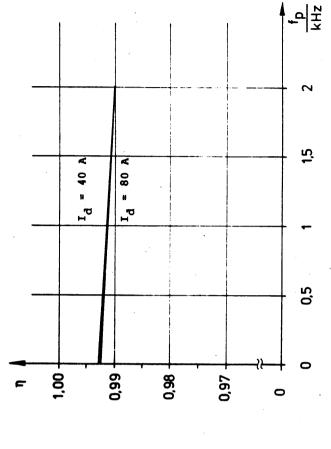

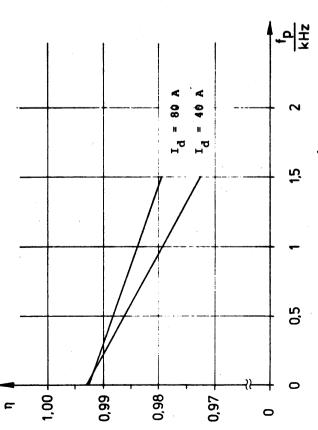

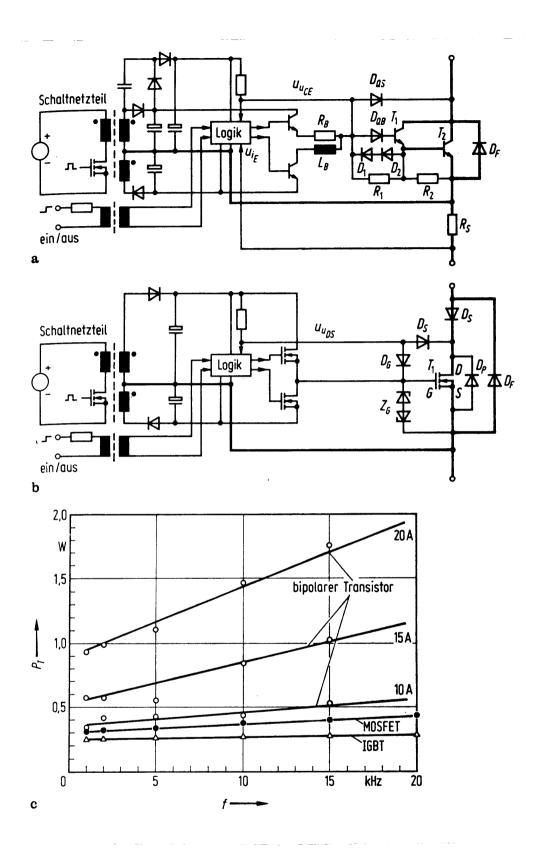

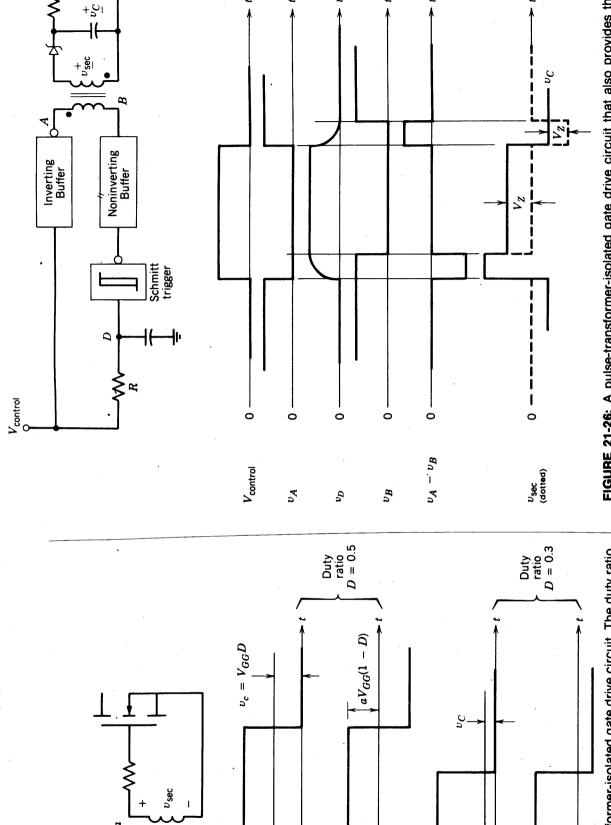

Als Beispiel für den Einfluss, den Fortschritte im Bereich der Bauteile bewirken, sei die Entwicklung von Gleichstromversorgungsgeräten über die letzten 40 Jahre aufgezeigt. In den frühen 50er Jahren ersetzten Halbleiterdioden Vakuumröhren, da unter anderem die Durchlassverluste dadurch von 30 Volt auf ca. 1 Volt reduziert und damit der Wirkungsgrad stark gesteigert werden konnte. Bis Mitte der 60er Jahre konnte die Schaltgeschwindigkeit von bipolaren Leistungstransistoren so gesteigert werden, dass Gleichstromumrichter - heute vielfach auch dc/dc-Konverter genannt - mit einer Schaltfrequenz von 10-20 kHz gefertigt werden konnten. Durch diese "Schaltreglertechnik" wurde der Wirkungsgrad gegenüber den Linearreglern drastisch gesteigert. In den späten 70er Jahren erlaubten Leistungs-MOSFETs einen wirtschaftlichen Einsatz im Frequenzbereich bei 200 kHz, wodurch die erreichbare Leistungsdichte erhöht werden konnte.

Vielfach waren es Bauteilneuerungen der Leistungshalbleiter Bauelemente, die starke Veränderungen in der Leistungselektronik bewirkten. Entsprechende Neuerungen sind für die nächsten Jahre wieder angesichts der neuen Halbleiter mit größerer Bandlücke (SiC, GaN) zu erwarten, denn nun stehen endlich auch erste Bauelemente z.V.. Zusätzlich hat die intensive Weiterentwicklung von Halbleiterbauelementen den Leistungsbereich von Stromrichtern deutlich erweitert.

## 1 Stromrichterventile, Leistungshalbleiterschalter und Simulationsmodelle

Die Stromrichtertechnik ist eines der wichtigsten Teilgebiete der Leistungselektronik.

Die wichtigsten Begriffe der SR-Technik sind definiert in der DIN 41750 "Begriffe für SR". Dort ist der Stromrichter (SR) definiert als:

Einrichtungen zum Stromrichten, wobei mit Stromrichten das Umwandeln einer oder mehrerer elektrischer Größen eines Stromsystems mittels SR-Ventilen verstanden wird. Elektrische Größen sind dabei Spannung, Strom, Frequenz incl. f = 0, Anzahl der Phasen. Umwandeln umfasst auch das Steuern elektrischer Energie.

Und ein SR-Ventil ist bezeichnet als:

- wesentlicher Bestandteil des SR und als

- Funktionselement, das elektrischen Strom nur in einer Richtung führt (Vorwärtsrichtung). Es kann aus mehreren in Reihe oder parallel geschalteten Elementen bestehen.

Beim Stromrichten wird es abwechselnd periodisch in den leitenden und in den gesperrten Zustand versetzt.

Es gibt *nichtsteuerbare* (Dioden) und *steuerbare* SR-Ventile, wobei bei den steuerbaren Ventilen unterschieden werden kann zwischen über Steueranschluß *abschaltbaren* Ventilbauelementen:

- a) GTO-Thyristoren (rückwärtssperrend, asymmetrisch, rückwärts leitend FCT, MCT)

- b) Transistoren (bipolar, BJT, MOSFET, IGBT, SIT)

und nur einschaltbaren Ventilbauelementen wie Thyristoren (rückwärtssperrend, asymmetrisch rückwärtsleitend, ASCR, RTL-Thyristor)

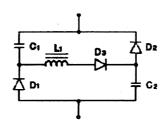

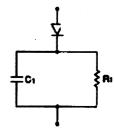

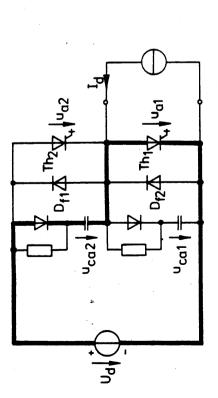

Die elektrische Verbindung der SR-Ventile und weiterer Funktionselemente wie z. B. Transformatoren, Saugdrosseln, Kommutierungseinrichtungenund Energiespeicher bilden die *SR-Schaltung*, die einen oder mehrere SR-Zweige enthält. Ein *SR-Zweig* enthält in der Regel SR-Ventil, Beschaltung und Zweigsicherung. Der konstruktive Aufbau eines SR-Ventils für eine SR-Schaltung einschließlich Verbindung, Beschaltung, Steuerimpulsübetrager, Sicherungen und ggf. Kühleinrichtungen wird SR-Satz oder Ventilsatz genannt. Der gesamte SR besteht in der Regel aus mehreren SR-Sätzen, SR-Transformator, Steuersätzen, Saugdrosseln, Kommutierungseinrichtungen, Energiespeicher, Filter und Entstörmittel und Hilfseinrichtungen

# 1.1 Klassifikation von Stromrichterventilen und Ventilbauformen

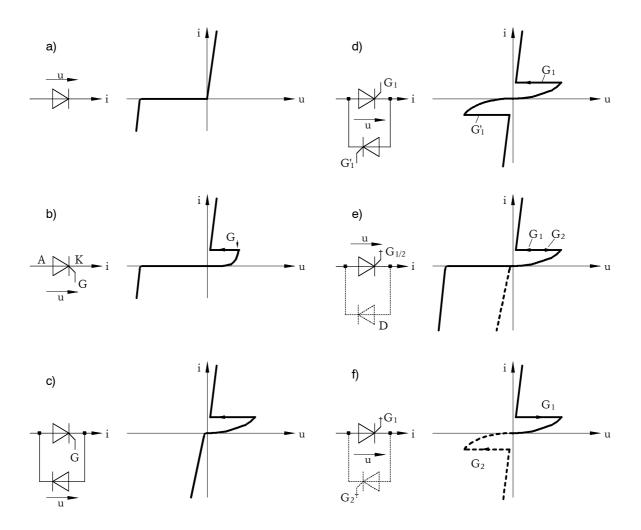

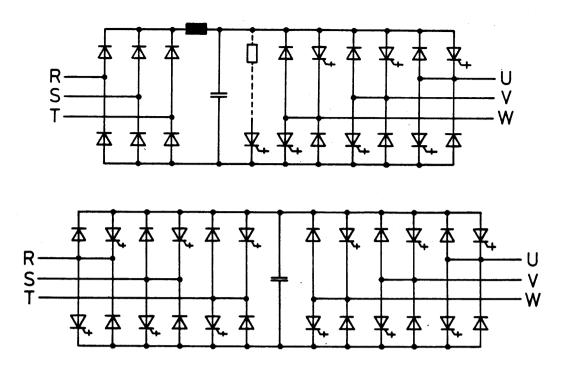

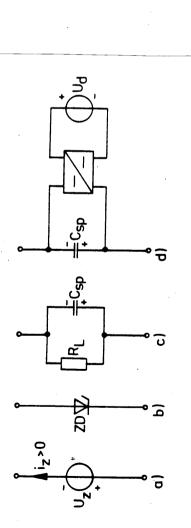

Bild 1.1: Stromrichterventilklassifikation

- a) nichtsteuerbares Ventil (Diode)

- b) einschaltbares elektronisches Ventil (Stromventil)

- c) Spannungsventil

- d) Zweirichtungsthyristor, einschaltbar

- e) ein- und ausschaltbares Ventil ( $G_1$  einschalten,  $G_2$  ausschalten)

- f) nur ausschaltbares Ventil

### 1.1.1 Ventilbauformen, konstruktive Eigenschaften

Die Siliziumtablette, die die Halbleiterstrukturen enthält, ist heute meist noch um genutzt zu werden in ein Gehäuse einzubringen.

Dessen Funktionen sind:

- a) die elektrischen Kontakte zwischen Hauptanschlüssen, Steueranschlüssen und Siliziumtablette herzustellen,

- b) die Verlustenergie in der Siliziumtablette in Form eines Wärmestromes zu einer Wärmesenke zu leiten und

- c) das Halbleitersystem gegen mechanische Beschädigung, elektrische Einflüsse und atmosphärische Umwelteinflüsse, die ein vorzeitiges Altern bewirken könnten, zu schützen.

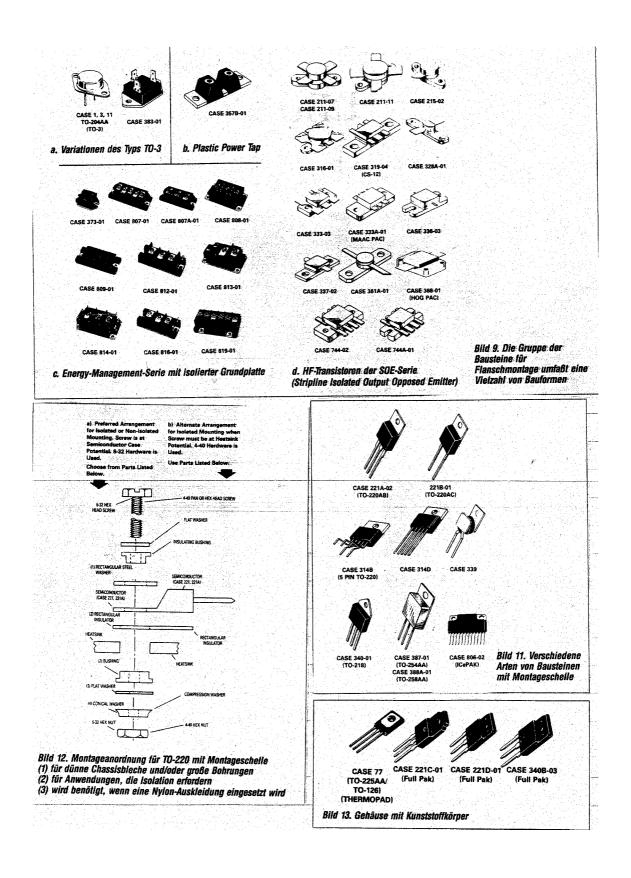

Die Gehäusebauformen sind im wesentlichen von b abhängig, so daß folgende Bauformen ausgeführt werden:

- kunststoffvergossene oder kunststoffumpreßte Halbleitersysteme mit oder ohne Kühlblech, wobei das Kühlblech häufig das Potential eines der Hauptanschlüsse hat (Kollektor, Drain; bei Dioden Anode oder Kathode); elektrische Anschlüsse durch Lötverbindungen (TO 220, 247)

- *vakuumdichte Metallgehäuse* mit Glasdurchführungen (je nach Einsatz Schraubgehäuse mit Sechskantboden, Einpreßgehäuse, TO 3, 5, ... 18 Flachgehäuse), Gehäuse auf Potential eines Hauptanschlusses

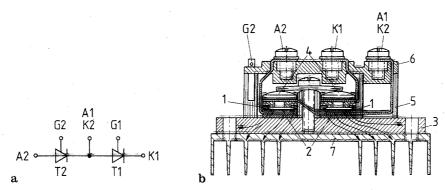

- Modulgehäuse: Kunststoffgehäuse mit Schraub- und Klemmvorrichtungen für Haupt- und Steueranschlüsse und metallische Grundplatte für Wärmeableitung. In einem Modul sind häufig zwei steuerbare Ventile und zwei Dioden d. h. eine WR-Phase integriert (SR-Zweig), aber auch Einzelelemente und komplette 3- Phasen-Wechselrichter (WR) sogenannte "6-Packs". Die einzelnen Silizium-Chips sind durch elektrisch gut isolierende, jedoch gut wärmeleitende Oxydkeramikplatten (Al<sub>2</sub>O<sub>3</sub>) an die potentialfreie, polierte und plane Bodenplatte kontaktiert (Module sind erhältlich von 20 500A)

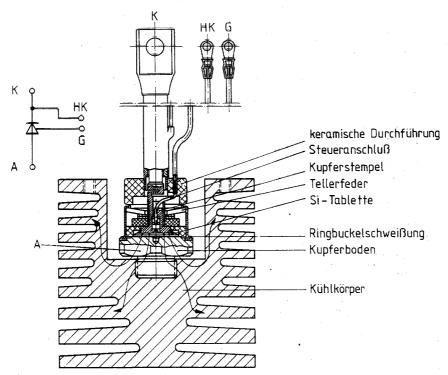

- *Schraub- und Flachbodengehäuse* mit Kupferboden, keramisch isolierten Durchführungen und Anschlußleitungen; der elektrische Anschluß zum Silizium-Chip erfolgt durch Druckkontakt, da die Lötverbindungen nicht wärmewechselfest sind für Ströme von 20 350A

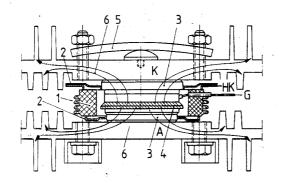

- Scheibenform, von denen die Wärme nach beiden Seiten abfließen kann. Das Gehäuse besteht aus einem Keramikring, der oben und unten durch elektrische Hauptanschlüsse in Form von Silberblechscheiben vakuumdicht verschlossen wird. Die Siliziumscheibe liegt dazwischen. Durch die obere Kontaktscheibe wird der "Gate"-Anschluß hergestellt und die Steuerelektrode wird druckkontaktiert durch eine Spannvorrichtung. Scheibenformen werden für Ströme > 150A eingesetzt.

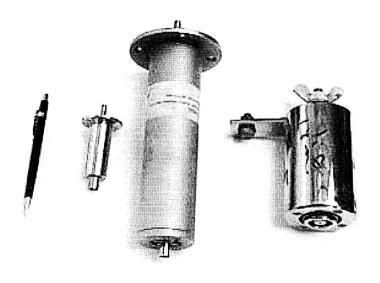

Grundsätzliche Darstellung eines Leistungshalbleiter-Moduls. a Schaltbild; b konstruktiver Aufbau und Wärmestrom; 1 Si-Tabletten, 2 Metalloxidscheiben, 3 potentialfreie Bodenplatte, 4 Druckkontaktelemente, 5 Kunststoffgehäuse, 6 Kunststoffdeckel mit Anschlußpunkten, 7 Kühlkörper

Grundsätzliche Darstellung eines Schraubgehäuses mit druckkontaktierter Siliziumtablette und des Wärmestromes von der Siliziumtablette in den Kühlkörper

Grundsätzliche Darstellung eines Scheibengehäuses mit durch die Einspannvorrichtung druckkontaktierter Siliziumtablette und des Wärmestromes von der Siliziumtablette zum Kühlkörper. 1 Keramikring, 2 Silberblech, 3 Kontaktscheiben, 4 SiTablette, 5 Spannvorrichtung, 6 Kühlkörper

## 1.2 Stromleitung in Metallen und Halbleitern

## 1.2.1 Übergänge zwischen Energieniveaus

Im thermischen Gleichgewicht entstehen pro  $cm^3$  und sec genausoviel Ladungsträger wie durch Rekombination wieder verschwinden. Man definiert die *Generationsrate* g als die Anzahl der pro Volumen und pro Zeit erzeugten Ladungsträger; entsprechend die <u>Rekombinationsrate</u> r als die pro Volumen und Zeit rekombinierenden Ladungsträger.

Die thermische Generationsrate wird mit  $g_{th}$  bezeichnet. Im thermischen Gleichgewicht ist

$$g_{th} = r \ln[m^{-3}s^{-1}].$$

Die Ladungsträger haben dann ihre Gleichgewichtskonzentrationen  $n_o$  bzw.  $p_o$ , für die gilt  $p_o \cdot n_o = n_i^2$ .

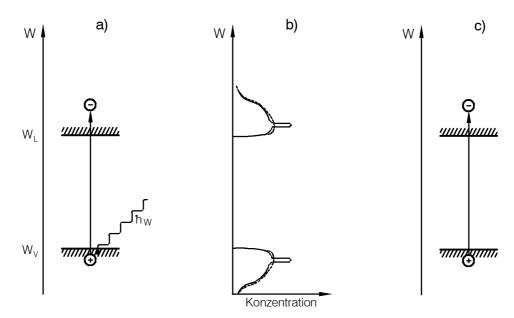

Wird das Gleichgewicht z.B. durch Einstrahlen von Licht gestört, für dessen Quantenenergie gilt  $\hbar \cdot w \ge w_L - w_V$ , so entstehen durch die Anhebung von Elektronen aus dem Valenzband in das Leitungsband zusätzliche Ladungsträger mit einer Generationsrate g (Bild 1.1).

Bild 1.2: Gleichgewichtseinstellung nach Bestrahlung eines Halbleiters a) Generation von Elektron-Loch-Paaren durch Lichtquantenabsorption b) Moment; Konzentrationsverteilung unmittelbar nach Absorption (durchgezogene Linie); Verteilung nach Einstellung des Gleichgewichts (gestrichelte Linie) c) Rekombinationsprozeß

Die *Bilanzgleichungen* lauten dann:

$$\frac{\partial n}{\partial t} = g(t) + g_{th} - r \tag{1.1}$$

$$\frac{\partial p}{\partial t} = g(t) + g_{th} - r \tag{1.2}$$

Die thermische Generationsrate wird i.A. nicht explizit berücksichtigt, man führt die Rekombinationsüberschußrate *R*

$$R = r - g_{th} \tag{1.3}$$

ein und macht den Ansatz, daß sie in erster Näherung der Abweichung vom Gleichgewicht proportional ist:  $R = \frac{n - n_o}{\tau} = \frac{p - p_o}{\tau}$ .

Die reziproke Proportionalitätskonstante  $\tau$  hat die Dimension einer Zeit und wird **Lebensdauer** der Ladungsträger genannt. Damit wird aus Gl. (1.1) und Gl. (1.2)

$$\frac{\partial n}{\partial t} = g - R = g - \frac{n - n_o}{\tau} \tag{1.4}$$

$$\frac{\partial p}{\partial t} = g - R = g - \frac{p - p_o}{\tau}.$$

(1.5)

Durch Integration von Gl. (1.4) und Gl. (1.5) erhält man für das Abklingen der überschüssigen Ladungsträgerkonzentration nach Abschalten der Störung zur Zeit t=0

$$n(t) - n_0 = [n(0) - n_0]e^{-t/\tau}$$

(1.6)

$$p(t) - p_0 = [p(0) - p_0]e^{-t/\tau}.$$

(1.7)

Im stationären Zustand  $\frac{\partial n}{\partial t} = \frac{\partial p}{\partial t} = 0$  gilt mi Gl. (1.4) und Gl. (1.5)

$$n = n_0 + g\tau$$

$$p = p_0 + g\tau$$

(1.8)

und

$$pn = p_0 n_0 + g\tau \cdot (p_0 + n_0) + (g\tau)^2 > n_i^2.$$

(1.9)

Bei einer Abweichung vom thermischen Gleichgewicht ist i.A.  $pn \neq n_i^2$ .

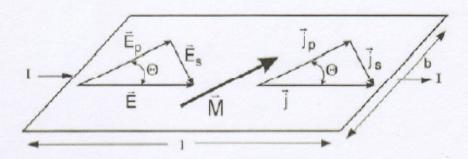

## 1.2.2 Driftgeschwindigkeit, Beweglichkeit, Leitfähigkeit

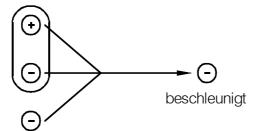

Unter dem Einfluß eines elektrischen Feldes  $\vec{E}$  werden Ladungsträger beschleunigt. Bei einem Stoß mit dem Kristallgitter werden sie wieder abgebremst. Es stellt sich eine mitte-

lere *Driftgeschwindigkeit*  $\dot{\vec{v}}_D$  der Ladungsträger ein, die proportional der Feldstärke ist. Für Elektronen ist

$$\dot{\vec{v}}_{n,D} = -\mu_n \cdot \vec{E} \,. \tag{1.10}$$

Für Löcher gilt

$$\dot{\vec{v}}_{p,D} = -\mu_p \cdot \vec{E} \,. \tag{1.11}$$

Die Proportionalitätsfaktoren  $\mu_{n, p}$  nennt man **Beweglichkeit** (Dimension  $m^2/Vs$ ). Die Stromdichte j ist

$$\dot{j} = -qn \cdot \dot{v}_{n,D} + qp \cdot \dot{v}_{p,D} = q(\mu_n n + \mu_p p) \dot{\vec{E}} = \sigma \dot{\vec{E}} . \tag{1.12}$$

In Gl. (1.12), dem Ohmschen Gesetz, wurde die *Leitfähigkeit* σ definiert zu

$$\sigma = q(\mu_n n + \mu_n p) . \tag{1.13}$$

### 1.2.3 Stoßzeit und Beweglichkeit

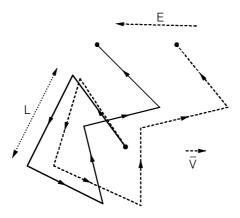

Die Beweglichkeit wurde oben nur phänomenologisch eingeführt. Sie soll nun auf atomistische Größen zurückgeführt werden. Ohne Feld bewegen sich die Elektronen auf Zickzack-Bahnen durch den Kristall (**Bild 1.2**). Zwischen zwei Stößen legen sie im Mittel die freie Weglänge L zurück. Dazu benötigen sie im Mittel die freie Flugzeit (sogenannte Stroßzeit)  $t_o$ .

Bild 1.3: Thermische Wärmebewegung ohne (durchgezogene Linie), mit elektrischem Feld (gestrichelte Linie)

Nach dem Gleichverteilungssatz der statistischen Mechanik haben freie Teilchen im Mittel die kinetische Energie

$$W_{kin} = \frac{1}{2}m \cdot \bar{v}^2 = \frac{3}{2}kT , \qquad (1.14)$$

wobei k... die Boltzmann-Konstante $(8, 6 \cdot 10^{-5} eV/K)$  und T... die Temperatur in Kelvin ist.

Daraus folgt für die Elektronen der quadratische Mittelwert der Geschwindigkeit, die sog. thermische Geschwindigkeit

$$v_{th} = \sqrt{\bar{v}^2} = \sqrt{\frac{3kT}{m}} \,. \tag{1.15}$$

Da keine Richtung bevorzugt ist, ist der Mittelwert der Geschwindigkeit  $\bar{v} = 0$ ; es fließt kein Strom.

Unter dem Einfluß eines elektrischen Feldes  $\vec{E}$  wird ein Elektron mit der Kraft  $\vec{F} = -q\vec{E}$  beschleunigt. Zwischen zwei Stößen beträgt der Geschwindigkeitszuwachs

$$\Delta \vec{v} = \Delta \vec{v}(t_0) - \vec{v}(0) = -\frac{q}{m} \vec{E} \cdot t_0. \tag{1.16}$$

Der mittlere Geschwindigkeitszuwachs in Feldrichtung ist

$$\Delta \bar{v} = \frac{v(t_0) - v(0)}{2} = \frac{-qt_0}{2m} \cdot E = -\mu E.$$

(1.17)

Für die Beweglichkeit wurde der Ausdruck gefunden:

$$\mu = \frac{qt_o}{2m}.\tag{1.18}$$

Im Halbleiter gilt speziell

$$\mu_n = \frac{qt_o}{2m_L}$$

,  $\mu_p = \frac{qt_o}{2m_V}$ . (1.19)

Dies ist jedoch nur solange richtig, wie die Driftgeschwindigkeit  $\bar{v}_D = \mu E \ll v_{th}$  oder die Feldstärke kleiner ist als die kritische Feldstärke

$$E_{krit} = \frac{1}{\mu} \sqrt{\frac{3kT}{m}}. ag{1.20}$$

Bei sehr großen Feldstärken nimmt die Zeit  $t_o$  zwischen zwei Stößen immer mehr ab, so daß die *Beweglichkeit* absinkt und sich eine Grenzgeschwindigkeit der Elektronen einstellt.

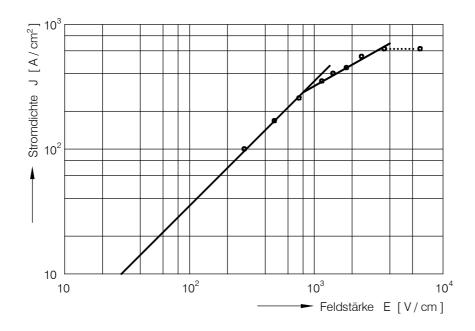

Bei Metallen ist  $E_{krit} \approx 10^5~V/cm$  und damit experimell nicht erreichbar, weil sie zu Stromdichten von  $10^9 A cm^{-2}$  und zum augenblicklichen Schmelzen des Kristalls führen würde. Das Ohmsche Gesetz gilt also uneingeschränkt. Bei Halbleitern tritt eine Abweichung vom Ohmschen Gesetz oberhalb  $\approx 10^3 V/cm$  auf (s. **Bild 1.3**).

Bild 1.4: Abweichung vom Ohmschen Gesetz bei Halbleitern

### 1.2.4 Temperaturabhängigkeit der Leitfähigkeit

Die Temperaturabhängigkeit der Leitfähigkeit  $\sigma$  bzw. des spezifischen Widerstandes  $\rho = 1/\sigma$  ist durch die Temperaturabhängigkeit der Konzentrationen n bzw. p und der Beweglichkeit  $\mu_n$  bzw.  $\mu_p$  gegeben.

In metallischen Leiterwerkstoffen ist die Zahl der Elektronen konstant. Die Beweglichkeit wird durch die Streuung der Elektronen an Gitterfehlern und Gitterschwingungen bestimmt. Der spezifische Widerstand setzt sich zusammen aus einem temperaturunabhängigen Anteil  $\rho_i$  der von der Streuung an Gitterfehlern herrührt, und einem Anteil  $\rho_G(T)$  der von den thermischen Schwingungen des Kristallgitters herrührt:

$$\rho = \rho_i + \rho_G(T). \tag{1.21}$$

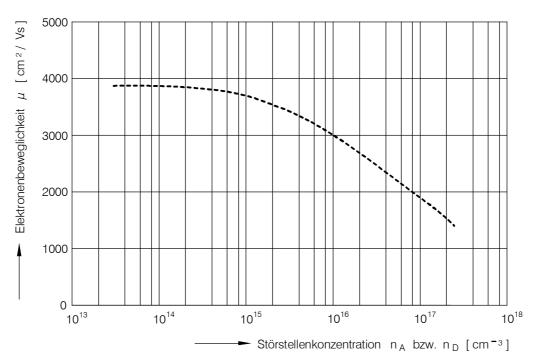

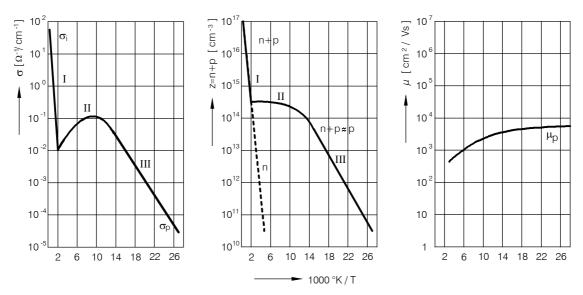

In Halbleitern werden die Elektronen und Löcher an Gitterschwingungen, Kristallfehlern und Störstellen sowie untereinander gestreut. Die Abhängigkeit der Beweglichkeit von der Störstellenkonzentration ist in **Bild 1.4** dargestellt. Die Leitfähigkeit über der Temperatur ist in **Bild 1.5** aufgetragen.

Bild 1.5: Abhängigkeit der Beweglichkeit von der Störstellenkonzentration

Bild 1.6: Leitfähigkeit, Konzentration und Beweglichkeit (der Löcher) von p-leitendem Silizium I = Eigenleitung, II = Störstellenerschöpfung, III = Störstellenreserve

### 1.2.5 Diffusionsströme in Halbleitern

In Metallen spielen Diffusionsströme keine Rolle, da Ladungsträgeranhäufungen immer

eine Raumladung bilden, die durch Feldströme abgebaut wird. Näheres in Kap. 1.2.8. Im Halbleiter gibt es jedoch positive und negative Ladungsträger, so daß neutrale Ladungsträgeranhäufungen entstehen können. Diese gleichen sich durch Diffusion aus.

Das Auftreten von Diffusionsströmen ist ein wesentliches Merkmal der Halbleiter und eine Voraussetzung für die Funktion vieler Bauelemente.

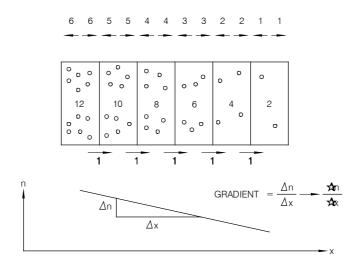

Die Teilchen strömen in Richtung des Konzentrationsgefälles (1. Ficksches Gesetz).

$$\frac{\overline{j_n}}{-q} = -D_n \text{ grad n; } \frac{j_n(x)}{-q} = -D_n \frac{dn}{dx} \text{ (eindimensional)}$$

(1.22)

$$\frac{\overline{j_p}}{q} = -D_p \quad \text{grad p}; \qquad \frac{j_p}{-q} = -D_p \frac{dp}{dx} \text{ (eindimensional)}$$

(1.23)

$D_{n,p}$  nennt man Diffusionskonstante (Dimension  $\frac{cm^2}{s}$ ).

In **Bild 1.6** ist dargestellt, wie ein lineares Konzentrationsgefälle zu einem konstanten Strom führt. Angenommen, in jedem Kasten fliegt die Hälfte der Teilchen nach rechts, die andere Hälfte nach links aus dem Kasten heraus; dann tritt insgesamt je ein Teilchen von links nach rechts durch die Trennwand.

Bild 1.7: Zur Erläuterung des Diffusionsstromes

## 1.2.6 Das Stromgleichungssystem im Halbleiter

Das Gleichungssystem umfaßt drei Gleichungstypen:

- a) die Stromgleichungen

- b) die Bilanzgleichungen

- c) die Poissongleichung

### A) Die Stromgleichungen

Die *Stromgleichungen* Gl. (1.24) und Gl. (1.25) sagen aus, daß ein Strom durch Felder und Konzentrationsgefälle verursacht wird:

$$\dot{j}_n = q \mu_n n \dot{E} + q D_n \quad \text{grad } n \tag{1.24}$$

$$\dot{j}_p = q \mu_p p \vec{E} - q D_p \quad \text{grad} \quad p \tag{1.25}$$

Gesamtstromdichte

$$j = j_p + j_n$$

(1.26)

### B) Bilanzgleichungen

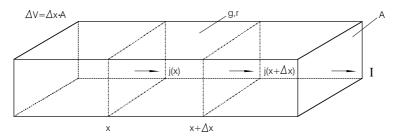

Die *Bilanzgleichungen* Gl. (1.4) und Gl. (1.5) müssen noch erweitert werden, wenn Ströme fließen. Die Zahl der Ladungsträger in einem Volumenelement dV kann auch erhöht werden, wenn mehr Ladungsträger hineinströmen als heraus. Diese Differenz wird durch die Divergenz des Stromes angegeben. In **Bild 1.8** ist dies dargestellt.

Bild 1.8: Zur Erklärung der Divergenz

Ladungsträgerzuwachs in  $\Delta V$  pro Zeiteinheit =  $-\frac{j(x + \Delta x)A - j(x)A}{\Delta x \cdot A}$

$$\lim_{\Delta x \to 0} \frac{j(x + \Delta x)A - j(x)}{\Delta x} = \frac{dj}{dx} = \text{eindimensionale Divergenz}$$

$$\frac{\partial n}{\partial t} = \frac{1}{q} \operatorname{div} \dot{j}_n - \frac{n - n_0}{\tau} + g \tag{1.27}$$

$$\frac{\partial p}{\partial t} = -\frac{1}{q} \operatorname{div} \dot{j}_p - \frac{p - p_0}{\tau} + g \tag{1.28}$$

## C) Die Poissongleichung

Die **Poissongleichung** verknüpft das Feld mit der Raumladungsdichte  $\rho_L$

$$\operatorname{div} \vec{E} = \frac{\rho_L}{\varepsilon_0 \varepsilon_r} = \frac{q}{\varepsilon_0 \varepsilon_r} (N_{D^+} - N_{A^-} + p - n)$$

(1.29)

Zur Lösung des Gleichungssystems müssen die Generationsrate g und die Randbedingungen gegeben sein.

### 1.2.7 Die Einsteinbeziehung

Als Anwendung des Gleichungssystems werde ein inhomogener dotierter Halbleiter betrachtet.

Voraussetzungen: thermodynamisches Gleichgewicht; d.h.

$$g = 0, j_n = 0, j_p = 0, \frac{\partial n}{\partial t} = 0, \frac{\partial p}{\partial t} = 0, \tag{1.30}$$

In eindimensionaler Darstellung resultiert ausGl. (1.24), Gl. (1.25)

$$0 = q\mu_n nE + qD_n \frac{dn}{dx}$$

(1.31)

$$0 = q\mu_p p E - q D_p \frac{dp}{dx} \tag{1.32}$$

$$\frac{dn}{dx} = \frac{q}{\varepsilon_0 \varepsilon_r} (N_{D^+} - N_{A^-} + p - n)$$

(1.33)

Mit den Lösungen

$$n = N_L \cdot e^{-(W_L - W_F)/kT} (1.34)$$

$$p = N_V \cdot e^{-(W_F - W_V)/kT}$$

(1.35)

und Gl. (1.31) nach E aufgelöst folgt:

$$E = -\frac{D_n}{\mu_n} \cdot \frac{1}{n} \cdot \frac{dn}{dx} = -\frac{D_n}{\mu_n} \cdot \frac{d(\ln n)}{dx} = \frac{D_n}{\mu_n} \cdot \frac{dW_L}{dx} \cdot \frac{1}{kT} . \tag{1.36}$$

Da  $W_L$  die potentielle Energie des Elektrons darstellt, ist  $-W_L/q$  das Potential V und  $\frac{1}{q} \cdot \frac{dW_L}{dx} = -\frac{dV}{dx} = E$  die elektrische Feldstärke

$$E = \frac{D_n q}{\mu_n \cdot kT} \cdot \frac{1}{q} \cdot \frac{dW_L}{dx} = \underbrace{\frac{D_n q}{\mu_n \cdot kT}}_{= 1} \cdot E$$

(1.37)

Somit resultieren die Einsteinbeziehungen

$$D_n = \mu_n \cdot \frac{kT}{q} \tag{1.38}$$

und analog

$$D_p = \mu_p \cdot \frac{kT}{q}. \tag{1.39}$$

### 1.2.8 Ausgleichvorgänge bei der Injektion von Ladungsträgern

#### a) Injektion von Elektronen in Metalle

In Metallen vereinfachen sich die Stromgleichungen, da es nur Elektronen gibt, zu:

$$j = \sigma E \tag{1.40}$$

$$\frac{\partial n}{\partial t} = \frac{1}{q} \operatorname{div} \, \mathbf{j} \tag{1.41}$$

$$\operatorname{div} E = \frac{\rho_L}{\varepsilon_0 \varepsilon_r} \tag{1.42}$$

Es möge eine zusätzliche Elektronenkonzentration  $\Delta n$  erzeugt werden, z.B. durch Elektro-

nenbeschuß

$$\frac{\partial n}{\delta t} = \frac{1}{q} \operatorname{div} j = \frac{1}{q} \operatorname{div} \sigma E = \frac{\sigma}{q} \operatorname{div} E = \frac{\sigma}{q} \cdot \frac{\rho_L}{\epsilon_0 \epsilon_r} = \frac{-\sigma q \Delta n}{q \epsilon_0 \epsilon_r} = \frac{-\sigma}{\epsilon_0 \epsilon_r} \cdot \Delta n$$

Lösung:

$$\Delta n = \Delta n(0) \cdot e^{-\frac{\sigma}{\varepsilon_0 \varepsilon_r} \cdot t} = \Delta n(0) \cdot e^{-\frac{t}{\tau_R}}$$

Der Ladungsüberschuß klingt mit der sogenannten dielektrischen Relaxationszeit (Bild 1.8)

$$\tau_R = \varepsilon_0 \varepsilon_r / \sigma$$

ab.  $(\tau_R < 10^{-14} s)$

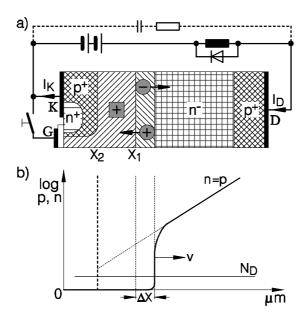

# b) Injektion von Elektronen in einen stark dotierten n-Halbleiter (Majoritätsträgerinjektion)

Es sei  $n \gg p$ . Damit ist

$$\sigma = q(\mu_n \cdot n + \mu_p \cdot p) \approx q\mu_n n = \sigma_n . \tag{1.43}$$

Der Elektronenüberschuß wird im wesentlichen durch den Feldstrom der Elektronen abgebaut. Es liegen ähnliche Verhältnisse vor wie im Metall. Die Relaxationszeit (s.**Bild 1.9**) beträgt somit

$$\tau_R = \frac{\varepsilon_0 \varepsilon_r}{\sigma_n}.\tag{1.44}$$

Beispiel: Ge:

$$\sigma = 10^2 \Omega^{-1} cm^{-1}$$

,  $\varepsilon_r = 16$ ,  $\tau_R \approx 10^{-14} s$

# c) Injektion von Elektronen in einen stark dotierten p Halbleiter (Minoritätsträgerinjektion)

Es sei  $p \gg n$ . Dann ist  $\sigma \approx q/\mu_p p = \sigma_p$ . Die Raumladung der injizierten Elektronen wird durch den *Feldstrom* der *Löcher neutralisiert*, aber nicht abgebaut. Die Neutralisation erfolgt mit der Zeitkonstanten

$$\tau_R = \frac{\varepsilon_0 \varepsilon_r}{\sigma_p}.\tag{1.45}$$

Es entsteht eine neutrale Anhäufung von Löchern und Elektronen. Diese Anhäufung kann nach Beendigung der Injektion nicht beliebig lange bestehen, sondern wird durch Diffusion und Rekombination abgebaut. Der *Konzentrationsausgleich* erfolgt dann viel langsamer als der *Raumladungsausgleich* (s. Bild 1.9).

Minoritätsträgerüberschüsse gleichen sich langsam aus gegenüber Majoritätsträgerüberschüssen.

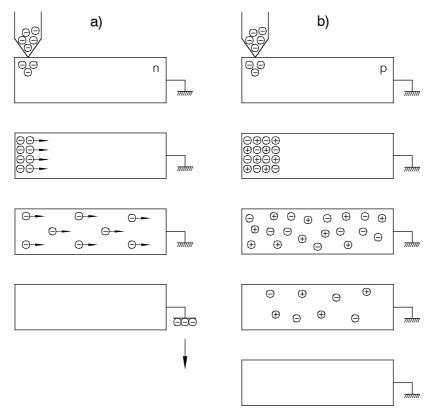

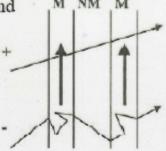

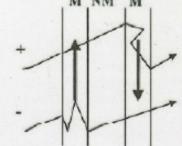

Bild 1.9: Veranschaulichung des Injektionsvorganges a) Metall oder Majoritätsträgerinjektion im HL

b) Minoritätsträgerinjektion

## 2 Modelle leistungselektronischer Halbleiterbauteile für die Schaltungssimulation

## 2.1 Einleitung: Anforderungen, Klassifikation, Status

Nachdem um 1990 eine Euphorie an Hochschulen und der Industrie, die sich mit Leistungselektronik befassen, herrschte, Modelle für die Leistungeelektronik zu generieren, die eine Simulation auf der Schaltungs- und Systemebene zulässt, hat sich diese Welle deutlich abgekühlt. Dies liegt wahrscheinlich daran, dass trotz drastisch gesunkener Kosten für Rechenleistung die hohen Ansprüche an die Modellierungstreue von bipolaren Leistungshalbleiter Bauelementen einerseits sowie die Kosten zur Herleitung der Modelle für verschiedene Näherungsniveaus sehr hoch sind, daß und andererseits die Vielfalt bei den magnetischen Komponenten und bei der Verbindungstechnik, z.B. der vor 10 Jahren gefertigten Stromrichtern enorm war. Nun hat der Kostendruck bei Stromrichtern geringer und mittlerer Leistung und Schaltnetzteilen und die Fortschritte im Bereich der Aufbau- und Verbindungstechnik für eine Verbreitung der on-board Bauweise gesorgt, so dass das Potential der Simulierbarkeit erhöht wird, wenn geeignete Modelle für Bauteile und PCBs mehrlagiger Platinen vorliegen.

Gegenwärtig werden für die Systemsimulation Verhaltensmodelle ganzer Stromrichter benötigt und für die Schaltungssimulation kompakte Modelle. Letztgenannte sollen im folgenden mehr charakterisiert werden. Zunächst zu einigen Anforderungen bzw. Randbedingungen:

- Der Entwurf kompakter Modelle soll sich immer an einem Kompromiss zwischen Genauigkeit und Simulationsgeschwindigdigkeit orientieren, aber es könnnen auch Level 1...4 Modelle zugelassen werden, die unterschiedliche Genauigkeitsansprüche z.B. befriedigen.

- Eine Reflektion der inneren Bauteilstruktur ist nur insofern von Interesse, wenn sie sich in messbaren elektrischen Verhalten äußert.

- Kompakte Modelle können basieren auf:

- Gleichungen, die vom physikalischen Bauteil abgeleitet wurden,

- Verhaltensdaten,

- Algorithmen zur Signalverarbeitung.

- Kompakte Modell werden implementiert mit Hilfe von

- Gleichungen

- Ersatzschaltungen (auch Makromodelle genannt).

Während der Entwurf hoch- und höchstintegrierter Schaltungen der Elektronik stark simulativ erfolgt, gestützt durch die Verfügbarkeit genauer kompakter Modelle, ist diese Vorgehensweise beim Entwurf leistungselektronischer Schaltungen noch nicht üblich. Das liegt vorwiegend an der Nichtverfügbarkeit von Standardmodellen (viele Bauteilmodelle gehören den Herstellern oder Großkunden, sind aber nicht allgemein verfügbar), an der Schwie-

rigkeit orts- und zeitabhängiger Größen, z.B. Rekombinationsvorgängen in Leistungshalbleitern oder Spulen in SPICE-basierenden Simulatoren zu implementieren und dem Aufwand und den Kosten für die Parameterextraktion. Gegenüber den Wünschen, für die jeweilige Anwendung ein passendes Modell der Leistungselektronikentwickler, was vom Hersteller bereits parametriert ist, aus einer Bauteilbibliothek aufzurufen, bleibt die Realität weit zurück. So misst bisher nur ein Simulatorhersteller physikalische Bauteile zur Extraktion von Parametern.

Die in Tabelle 1 gezeigt Übersicht gibt Aufschluß über Eigenschaften und Anwendungen von Modellen, die das ideale genäherte und genaue Schaltverhalten wiederspiegeln, ergänzt um solche, die das thermische-, fehlerhafte- und alterungsbedingte Verhalten beschreiben.

| Modelltyp           | Eigenschaften                                                                                                                                                         | Anwendungen                                                                                                                                                                 | Unterstützt<br>von Produkt                   |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Idealer<br>Schalter | Statisches Durchlaßverhalten, ideales Schaltverhalten                                                                                                                 | Simulation vieler Schaltzyklen, Unternehmung des Systemverhaltens, Festlegung des eingeschwungenen Betriebspunktes                                                          | EMTP, PSIM,<br>SABER,<br>ELDO, SIM-<br>PORER |

| Basisschal-<br>ter  | Statisches und dynamiches<br>Bauteilverhalten, kurze Si-<br>mulationszeiten dank ein-<br>facher Modellgleichungen,<br>einfache Parametrierbar-<br>keit durch Anwender | Weiteres Einsatzfeld,<br>wenn genähertes Schalt-<br>verhalten ausreichend                                                                                                   | SABER,<br>ELDO,<br>SIMPORER                  |

| Exakter<br>Schalter | Genaue Wiedergabe des<br>statischen u. dynamischen<br>Bauteilverhaltens inner-<br>halb der SOA                                                                        | Bestimmung der Schaltver luste, Entwurf von Entlastungsnetzwerken, Untersuchung der Schaltbelastung innerhalb der SOA bei Vorgabe von wertenparasitärer Schaltungselementen | SABER,<br>ELDO                               |

| Thermik             | Thermisches Ersatzmodell<br>erlaubt die Bestimmung<br>der Sperrschichttempera-<br>tur bei Lastwechseln                                                                | Kühlkörperentwurf, Berechnung des thermischen Stresses, der therm. Stabilität bzw. Instabilität                                                                             |                                              |

| Fehlerfall          | Betrieb ausserhalb der<br>SOA führt zu einstellba-<br>rem Fehlerverhalten                                                                                             | Analyse von Kurzschlussfall, Unterbrechung thermischer Instabiltät, Bestrahlung                                                                                             | teilw. SABER                                 |

| Alterung            | Alterungseffekte infolge<br>elektrischer-, thermischer<br>Strahlungsbelastung                                                                                         | Zuverlassigkeitsanalysen                                                                                                                                                    |                                              |

## 2.2 Durchlaßverhalten der Leistungsdiode

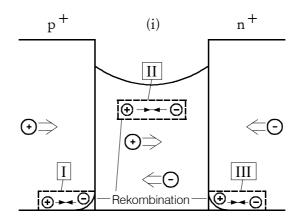

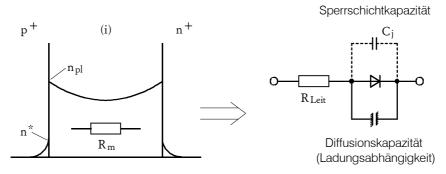

Der Durchlaßstrom wird nur durch Rekombination bestimmt. Von links startet ein Löcherstrom und wird in der (i)-Zone nach Rekombination am anderen Ende zu einem Elektronenstrom:

Bild 2.1:

Löcherstrom

$$\rightarrow$$

Elektronenstrom  $i_h \rightarrow i_{el}$  (2.1)

Schematische Einteilung:

Der Gesamtstrom setzt sich aus drei Einzelströmen zusammen.

$$i = \underbrace{i_{rek}(p^+)}_{I} + \underbrace{i_{rek}(i)}_{II} + \underbrace{i_{rek}(n^+)}_{III}$$

(2.2)

Bei hochdotiertem Silizium (Dotierungskonzentration > 10<sup>17</sup> cm<sup>-3</sup>) gilt:

- Die Beweglichkeit der Ladungsträger geht zurück. Die Beweglichkeit der Elektronen fällt von ca. 1500 cm/Vs in einem schwach dotiertem Gebiet auf den Wert von 300 ... 500 cm/Vs im stark dotiertem Emitter ab.

- Der Bandabstand wird verringert in der Größenordnung von z.B. 10 ... 100 meV. Damit beträgt der Bandabstand im hochdotierten Silizium 1,1...l eV (Die Daten für das Bandgap Narrowing sind noch nicht völlig gesichert).

n<sup>+</sup> - Gebiet:

Die intrinsische Ladungsträgerkonzentration kann mit den Zustandsdichten beschrieben werden:

Allgemein:

$$N_{V} \cdot e^{-\frac{E_{g}}{kT}}$$

$$\text{2.3}$$

$$\text{2.3}$$

$$\text{2.3}$$

$$\text{2.3}$$

+-Zeichen?) =

$$N_c \cdot N_V \cdot e^{-\frac{E_g - \Delta E_g}{kT}}$$

+-Zeichen?) =  $n_1^2 \cdot e^{-\frac{\Delta E_g}{kT}}$  (2.4)

?Symbol-Satz? $\Delta E_g \approx 10...1$

Bei einer starken Dotierung muß man mit einer Bandabstandsverminderung von 10 ... 100 meV rechnen. Schon nur bei  $\Delta E_g = 30$ meV ergibt sich ein Faktor von 3.

#### i - Gebiet:

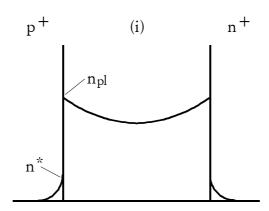

Bild 2.2:

$$p_{pl}(i) \cdot n_{Pl}(i) = n_{pl}^{2}$$

$$= n_{i}^{2} \cdot e^{\frac{U_{i}}{V_{T}}}$$

(2.5)

?Pfeil-oben? [siehe auch Formel (4

p<sup>+</sup> - Gebiet:

$$p_0 \cdot n^* = \underbrace{n_i^2 \cdot e^{\frac{U_i}{V_T}}}_{n_{pl}^2} \cdot e^{\frac{\Delta E_g}{kT}}$$

$$(2.6)$$

$$\Rightarrow n^* = \frac{n_{pl}^2}{p_0} \cdot e^{\frac{\Delta E_g}{kT}} \tag{2.7}$$

- Die Trägerlebensdauer nimmt durch die erhöhte Dotierung ab. (Genauere Angaben findet man in Standardlehrbüchern)

- Die Trägerlebensdauer wird wegen der hohen Dotierung durch die Auger-Rekombination bestimmt.

n<sup>2</sup>p - Prozeβ:

Bild 2.3:

Es rekombinieren also zwei Elektronen mit einem Loch unter Abgabe eines beschleunigten Elektrons. Es gibt auch einen p<sup>2</sup>n-Prozeß, bei dem zwei Löcher mit einem Elektron rekombinieren unter Abgabe eines beschleunigten Loches.

$$uger = \begin{cases} \frac{1}{10^{-31} \frac{cm^{-6}}{s} \cdot N_D^2} & \text{in } n^{?+-\text{Zeiche}} \\ \frac{1}{10^{-31} \frac{cm^{-6}}{s} \cdot N_A^2} & \text{in } p^{?+-\text{Zeiche}} \end{cases}$$

(2.8)

## 2.3 Strom- und Ladungsdichten

*Bild 2.4:*

$$\frac{(p^{?+-\text{Zeichen}?}) + j_{rek}(i) + j_{rek}(n^{?+-})}{\frac{(p^{?+-\text{Zeichen}?})}{p^{?+-\text{Zeichen}?}}} + \frac{Q_s(i)}{\tau(i)} + \frac{Q_s(n^{?+-\text{Zeichen}?})}{\tau(n^{?+-\text{Zeichen}?})}$$

(2.9)

$$Q_{s}(p^{?+-\text{Zeichen}?}) = k_{p^{?}}$$

$$Q_{s}(n^{?+-\text{Zeichen}?}) = k_{n^{?}}$$

(2.10)

$$\frac{Q_{s}(i)}{\tau(i)} + Q_{s}^{2}(i) \cdot \left(\frac{k_{p^{2+-\text{Zeichen?}}}}{\tau(p^{2+-\text{Zeichen?}})} + \frac{k_{n^{2+-Z}}}{\tau(n^{2+-Z})}\right)$$

(2.11)

- Bei hohen Stromdichten üerwiegt <sup>·Zeichen?</sup>,  $p^{?+-}$ . Das bedeutet, daß die Ladungsträger durch das gesamte i-Bahngebiet hindurch strömen und erst im jeweils komplementär dotierten Gebiet rekombinieren.

Durchlaßspannung der idealen p-i-n Diode:

$$U_F = U_j + U_m \tag{2.12}$$

$U_m$ : Ohmsche Spannung im i-Gebiet (Spannung, die am Widerstand des i-Bahngebietes  $R_m$  abfällt).

• Bei niedrigen Stromdichten:

$$Q_S(i) \sim j \tag{2.13}$$

$$R_m \sim \frac{1}{j} \tag{2.14}$$

$$\Rightarrow U_m = \text{constant}$$

(2.15)

D.h. der Bahnwiderstand geht in dem Maße zurück wie der Strom

• bei hohen Stromdichten:

Bild 2.5:

$$Q_S(i) \sim \sqrt{j} \tag{2.16}$$

$$R_m \sim \frac{1}{\sqrt{j}} \tag{2.17}$$

$$\Rightarrow U_m = \sqrt{j} \tag{2.18}$$

Diese Eigenschaft wird also von der Speicherladung bestimmt.

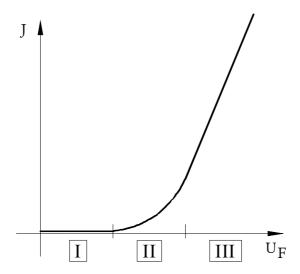

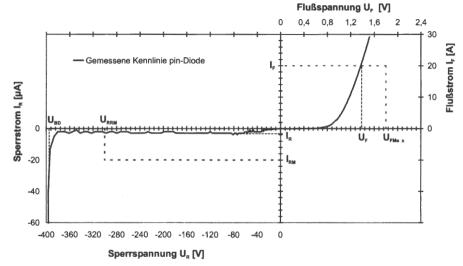

### 2.4 Durchlaßkennlinie

Damit ergibt sich die Durchlaßkennlinie der Leistungsdiode wie folgt:

Bild 2.6:

介

Für die einzelnen Bereiche ( I .... III ) der Kennlinie ergeben sich dann folgende Zusammenhänge:

I

Extrem kleine Stromdichte ⇒ Shockleysche-Kennliniengleichung

$$U_{j}$$

Pfeil-Unten?  $J = J_{s} \cdot \left(e^{\frac{U}{V}}\right)$

$$\left(V_{T} \cdot \ln \frac{J + J_{s}}{J_{s}}\right)$$

(2.19)

• II Niedrige Stromdichte (typ. 1*A/cm*<sup>2</sup>

$$U_{F} = U_{j} + \underbrace{U_{m}}_{const.}$$

(einige 0,1V)

• III

Hohe Stromdichte (Betriebsstromdichte  $\approx 100 \text{A/cm}^2$ )

$$U_{F} = U_{j} + \underbrace{C \cdot \sqrt{J}}_{m}$$

$$(2.21)$$

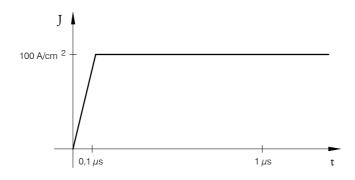

## 2.5 Einschaltverhalten der Leistungsdiode

Übergang vom stromlosen Zustand in den Durchlaßbetrieb

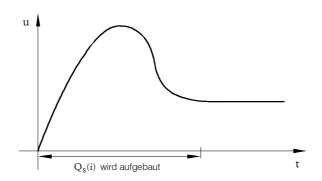

Bild 2.7:

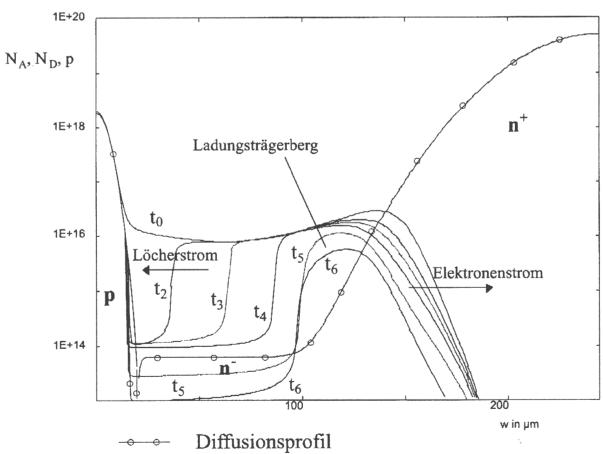

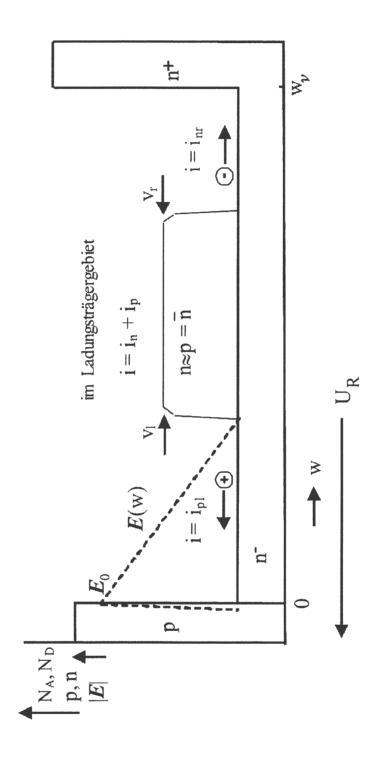

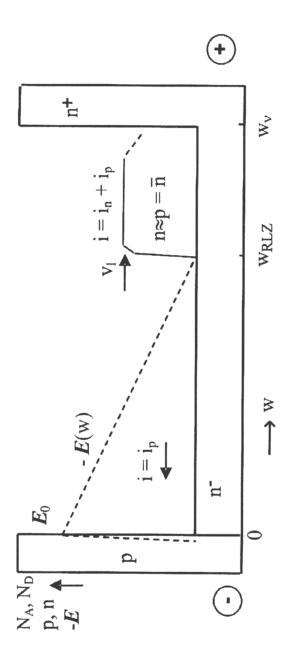

Wenn auf eine Leistungsdiode ein starker Vorwärtsstrom aufgeschaltet wird (hier: bis 100 A/cm² in 0,1 µs ), ist das schwach dotierte Zwischengebiet (n⁻ bzw. i) zuerst noch nicht gut leitfähig, weil sich dort nur wenige freie Ladungsträger befinden. Durch diese geringe Leitfähigkeit fällt über der Diode zuerst eine relativ hohe Spannung in Durchlaßrichtung ab. Der Vorwärtsstrom bewirkt dann, daß viele Ladungsträger in das schwach dotierte Gebiet injiziert werden und das Elektron-Loch-Plasma sich aufbaut. Durch die hohe Injektion wird der Durchlaßwiderstand der Leistungsdiode stark verringert und an ihr kann dann nur noch eine geringe Spannung abfallen. Ab ca. 1µs stellt sich dann ein stationärer Wert für die Durchlaßspannung ein. Dieser Wert ist maßgeblich für die Vorwärtskennlinie der Leistungsdiode.

Bei Dioden für Sperrspannungen bis ca. 100 V ist das n - Gebiet auch ohne Plasmaüberschwemmung gut leitfähig, da das Zwischengebiet relativ stark dotiert werden kann.

⇒ Keine Einschaltüberspannung

⇒ Relativ geringe Speicherladungseffekte

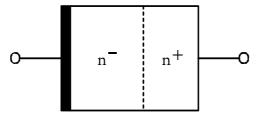

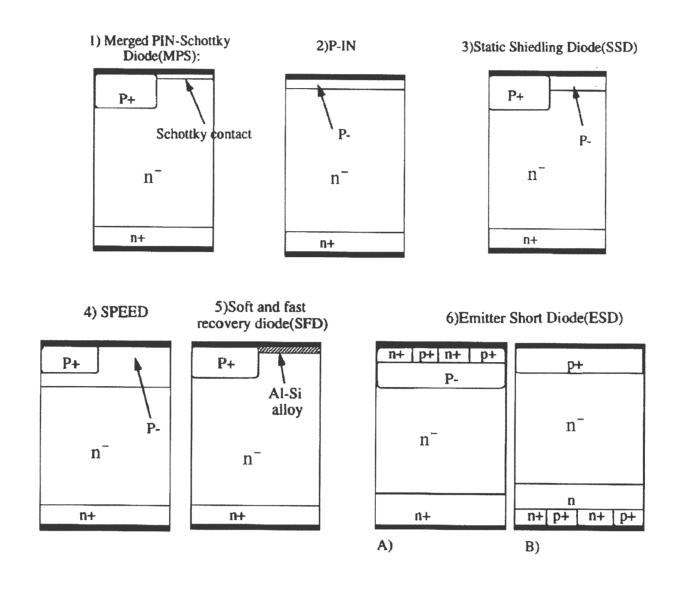

## 2.6 Sonderfall der schnellen Diode: Die Schottky-Diode

Die Schottky-Diode wird für Spannungen ≤ 100 V eingesetzt.

Bild 2.8:

- Sperrverhalten: Sehr hohe Sperrströme, die mit der Sperrspannung sehr stark ansteigen. (Nachteil)

- Keine Minoritätsladungsträger-Injektion. → Keine Speicherladung. (Vorteil)

- Eine Leitfähigkeits-Modulation ist daher nicht möglich. (Nachteil?)

- Typischer Wert der Diodenknickspannung  $U_{knick} = 0.3 \dots 0.35V$

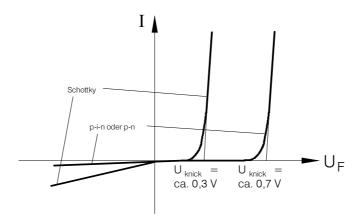

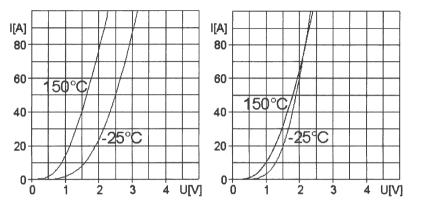

Damit ergeben sich folgende charakteristische Kennlinien für die beiden Diodentypen.

Bild 2.9:

## 3 Abschaltbare Bauelemente der Leistungselektronik

Gegenwärtig ist bei abschaltbaren Leistungsbauelementen ein bemerkenswerter Aufschwung im Gange. Aufgrund technologischer Fortschritte ist es möglich geworden, feinstrukturierte bipolare- und MOS/Bipolar-Bauelemente großer Chipfläche herzustellen. Es wird versucht, Möglichkeiten und Grenzen dieser Bauelemente aufzuzeigen. Dazu werden nach einer Erläuterung des Funktionsprinzips die Vorgänge beim Schalten analysiert. Besondere Beachtung wird dem Auftreten kritischer Zustände gewidmet, die zu einer Störung der Funktionsfähigkeit führen können, und die für die Festlegung der Grenzen von Strom- und Spannung sowie deren Anstiegsgeschwindigkeiten verantwortlich sind. Abschließend werden die Bauelemente miteinander verglichen.

## 3.1 Einleitung

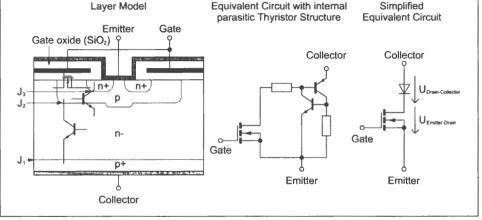

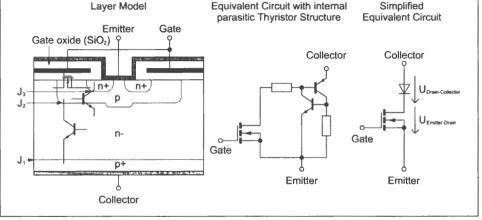

Leistungs-Halbleiterbauelemente werden vorwiegend als elektronische Schalter eingesetzt. Vorteilhaft sind Bauelemente, die man *nicht* nur über das Gate ein- sondern auch *ausschalten* kann. Mit ihnen läßt sich der leistungselektronische *Schaltungsaufwand* erheblich *verringern*. Bis etwa 1985 gab es hierfür nur den bipolaren Transistor und den abschaltbaren Thyristor GTO(gate turn off-Tyristor) . Hinzu kam, daß der Transistor nur im unteren Leistungsbereich eingesetzt werden konnte. Inzwischen haben sich die Verhältnisse grundlegend geändert. Zum einen konnte die *Leistungsgrenze* des *bipolaren Transistors* deutlich erhöht werden, zum anderen haben Transistor und GTO durch Feldeffekt-Bauelemente *Konkurrenz* bekommen. Im Spannungsbereich unterhalb 600 V vor allem durch den Leistungs-MOSFET und bei höheren Spannungen durch den *FCTh* (Field Controlled Thyristor) und den *IGBT* (Isolated Gate Bipolar Transistor).

Sowohl der FCTH als auch der IGBT lassen sich sehr schnell ein- und ausschalten. Der *FCTh* verfügt über die höhere Stromtragfähigkeit und den größeren Überlaststrom, der *IGBT* über die leichtere Ansteuerbarkeit und das bessere Kurzschlußverhalten. Beide Bauelemente bestehen aus integrierten Einzelzellen mit Kantenlängen im Mikrometerbereich und benötigen zur *Fertigung* eine *IC-Technologie*.

Andererseits lassen sich durch die *Nutzung der IC-Technologie* auch bei GTO's und bipolaren Transistoren durch feinstrukturierten Zellenaufbau die *Schalteigenschaften verbessern*. Viele Tagungsbeiträge gehen im einzelnen auf die Leistungsfähigkeit der Bauelemente, die Bauformen, die technologische Herstellung, die Einsatzbereich und die Entwicklungstendenzen ein. Im Rahmen des Kapitels beschränkt sich die Betrachtung demgegenüber auf die *grundsätzlichen Vorgänge*. Sie versucht, einen Einblick in die Funktionsprinzipien zu vermitteln und in die Probleme der abschaltbaren Bauelemente einzuführen. Das *Interesse* gilt dabei einerseits Bauelementen, die für den Einsatz am *400 V-Netz* geeignet sind, und die dementsprechend mehr als 1000 V zu sperren vermögen. Andererseits werden Mosfets Cool- FETs ebenfalls betrachtet, weil sie für die einphasige Stromrichterschaltungen nicht mehr wegzudenken sind.

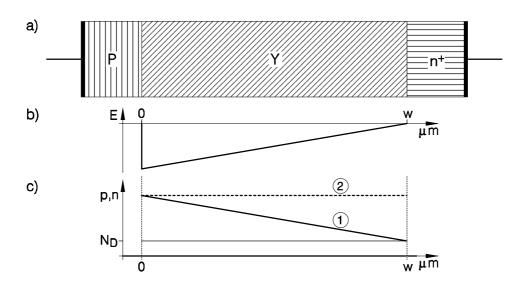

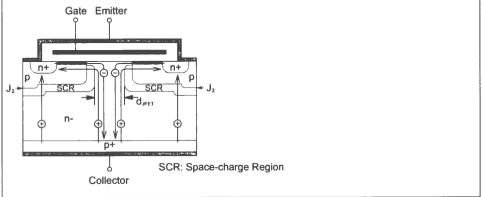

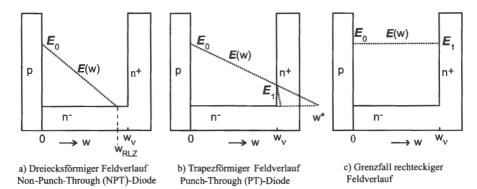

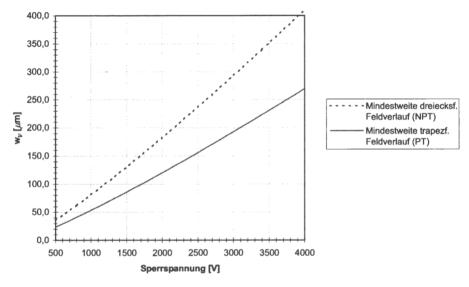

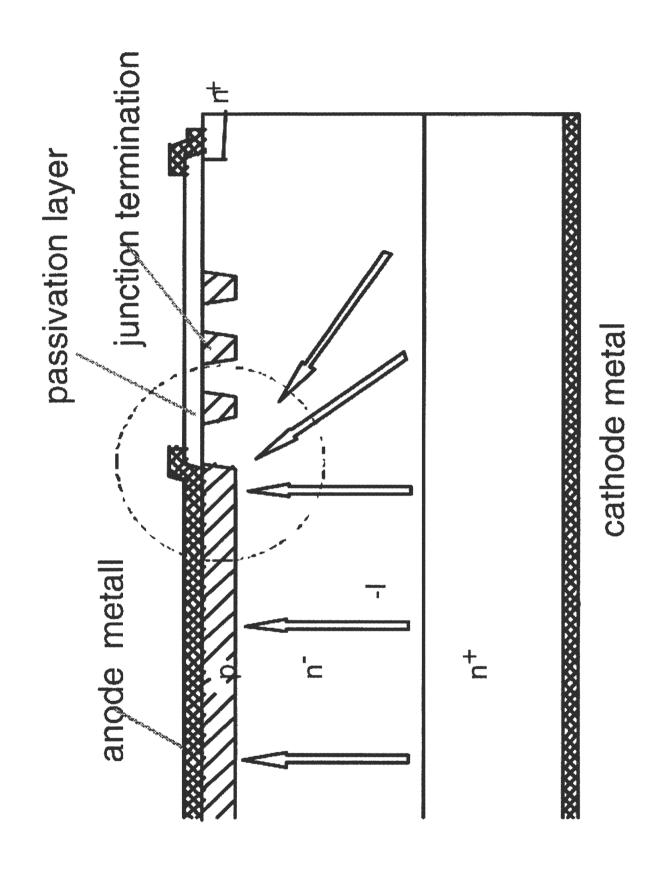

### 3.1.1 Allgemeine Anforderungen

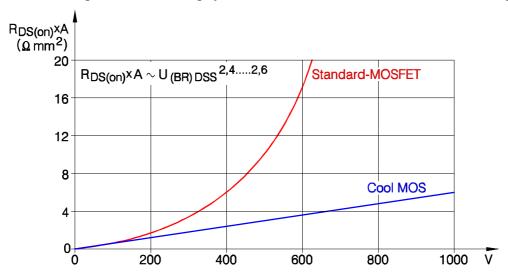

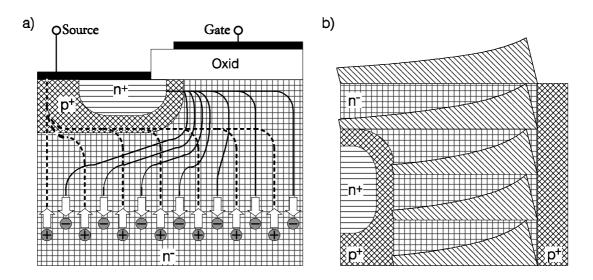

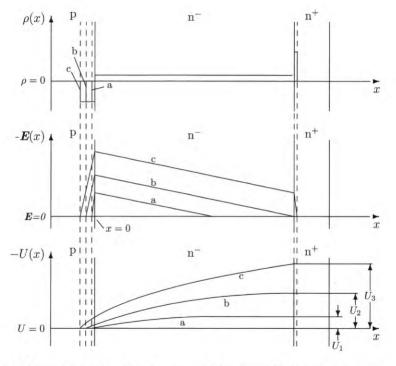

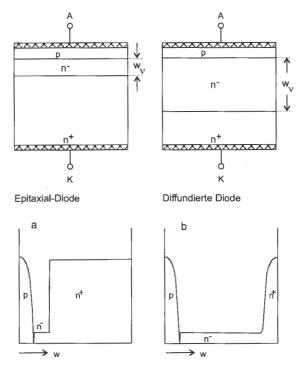

Halbleiterbauelemente für hohe Sperrspannungen benötigen eine eigens dafür vorgesehene Zone, in die sich die Raumladungszone ausdehnen kann (Bild 3.1). Die Weite muß um so größer und die Dotierungskonzentration  $N_D$  um so kleiner sein, je höher die aufzunehmende Sperrspannung ist. Der ohmsche Widerstand dieser Zone ist dem Verhältnis  $w/N_D$  proportional und nimmt nach dem Potenzgesetz

$$R = U_B^{2,5} (3.1)$$

mit der Durchbruchspannung  $U_B$  zu, wegen  $w \approx U_B^{7/6}$  und  $N_D \approx U_B^{-4/3}$ . Bei einer Steigerung der Sperrfähigkeit von z.B. 400 V auf 1000 V, d.h. um den Faktor 2,5, nimmt R um das Zehnfache zu. Das ist der Grund, weshalb Hochvolt-MOS-Transistoren sehr große On-Widerstände aufweisen und für Anwendungen im Hochstrombereich weniger geeignet sind.

Bild 3.1: pn-Übergang im Sperr- und Flußfall

- a) Schichtenfolge (p... Anode, +... Verarmunszone, n<sup>+</sup>...Kathode

- b) Elektrische Feldstärkeverlauf

- c) p/n ... Löcher-/Elektronenkonzentation

Damit im Flußfall keine übermäßigen elektrischen *Verluste* entstehen, ist es notwendig, den Widerstand der Zone mittels *Injektion* von *Minoritätsträgern* zu verkleinern. Zur wirkungsvollen Anhebung der *Ladungsträgerdichte* (*Leitfähigkeitsmodulation*) muß die Diffusions-

länge N etwa gleich w sein. Daraus folgt, daß die Trägerlebensdauer  $\tau$  wegen  $\tau \approx L^2$  dem Quadrat der Zonenbreit w proportional ist

$$\tau \approx w^2. \tag{3.2}$$

#### Hochvoltbauelemente erfordern deswegen eine große Trägerlebensdauer.

Beim Einschalten des Stromes dauert es eine gewisse Zeit, bis der Injektionsstrom die Überschußträgermenge zugeführt hat. Wenn die Minoritätsträger auf der einen Seite der N-Zone einströmen und auf der anderen Seite nicht abfließen können, weil sie z.B. durch eine

Potentialbarriere daran gehindert werden ( $P^+N^-N^+$  - Diode), dann *stauen sie sich auf* (Kurve 2, **Bild 3.1** c), bis genau so viele durch Rekombination verschwinden, wie zufließen. Folglich gilt  $I_F = Q/\tau$ , bzw.

$$Q = \tau \cdot I_F, \tag{3.3}$$

wobei  $I_{Fe}$  der Flußstrom und Q die Speicherladung sind. Die Speicherladung ist in diesem Fall der Trägerlebensdauer sowie dem Strom proportional. Der *Einschaltvorgang* dauert damit *um so länger*, je *größer* die *Lebensdauer* ist.

Kurze Ein- und Ausschaltvorgänge erfordern somit eine kleine Trägerlebensdauer. das steht im Gegensatz zu den Anforderungen, die sich aus dem Durchlaß- und Sperrverhalten ergeben. Dieser Gegensatz gilt im Prinzip für alle bipolaren Bauelemente, unabhängig von der Zahl der pn-Übergänge. Der unumgängliche Kompromiß bei der Herstellung hochsperrender Bauelemente bietet jedoch bei den unterschiedlichen Typen verschieden großen Spielraum für eine optimale Abstimmung von statischen und dynamischen Eigenschaften.

## 3.2 Bipolarer Transistor

#### 3.2.1 Statisches Verhalten

Leistungstransistoren haben heute in der Regel eine npvn-Zonenfolge (Bild 3.2). Der Kollektor besteht aus der schwach dotierten n-Zone, abgekürzt  $\upsilon$  und der hochdotierten n<sup>+</sup>-Zone. Die  $\upsilon$ -Schicht dient zur Aufnahme der Kollektorspannung. Für ihre Weite  $w_C^* = w_C - w_B$  gilt näherungsweise die Beziehung

$$\frac{w_C^*}{\mu m} = 10^{-1} \frac{U_{CEO}}{V}$$

(3.4)

spannungen erzielen (Punkt E<sub>2</sub>, Bild 3.4). Erforderlich ist allerdings eine *hinreichende Übersteuerung*.

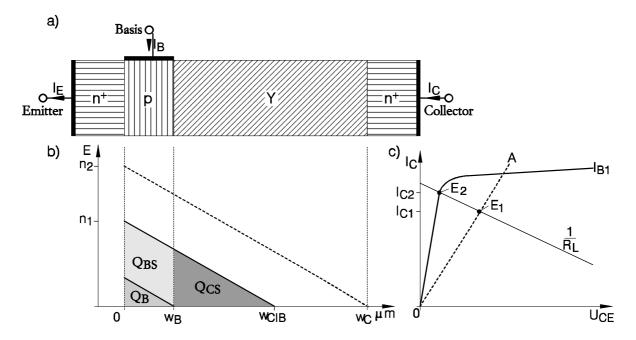

Bild 3.2: Hochvolttransistor a) Aufbau, b) Trägerverteilung und c) Kennlinie

Leider wirkt sich die Basisaufweitung ungünstig auf die Emitter-Stromverstärkung  $h_{FE}$  aus. Sie führt zu einem charakteristischen Abfall von  $h_{FE}$  bei hohen Kollektorströmen mit  $I_C^{-1}$ . Das hat folgende Ursache: Der Kollektorstrom ist dem Gradienten der Elektronendichte n sowie der Emitterfläche A proportional,  $I_C \approx A \cdot n_1/w_B \approx A \cdot n_2/w_C$ . Bei einer Basisaufweitung bis  $w_C$  ist der Randwert  $n_2$  am Emitter erheblich größer als ohne Basisaufweitung,  $n_1$ . Hinzu kommt, daß der Löcherstrom von der Basis zum Emitter proportional zu  $n^2(0)$  ist und bei hohen Randwerten den Hauptteil des Basisstromes aufmacht. Näherungsweise gilt daher  $I_B \approx n_2^2 \approx (I_c \cdot w_c/A)^2$ , woraus man für  $h_{FE}$  mit  $w_C \approx U_{CBO}^{7/6}$  den Zusammenhang gewinnt

$$h_{FE} \approx A \cdot I_C^{-1} \cdot w_C^{-2} \approx A \cdot I_C^{-1} \cdot U_{CR0}^{-2, 3}$$

(3.5)

Die Beziehung Gl. (3.5) zeigt neben dem  $I_C^{-1}$ -Abfall einen noch stärkeren Abfall mit der Kollektor-Basis-Durchbruchspannung  $U_{CB0}$  und bringt ein grundsätzliches Problem des Leistungstransistors zum Ausdruck: Damit die Stromverstärkung nicht zu klein wird, muß die *Fläche* bei einer Erhöhung der Sperrspannung und des Stromes *beträchtlich vergrößert* werden. Aus diesem Grund arbeiten Hochvolttransistoren bei einer geringen Stromdichte. Sie beträgt z.B. in den heutigen 1400 V-Transistoren mit 25 A/ $cm^2$  und ist damit um fast eine Zehnerpotenz niedriger als im GTO und im FCTh.

### 3.2.2 Schaltverhalten

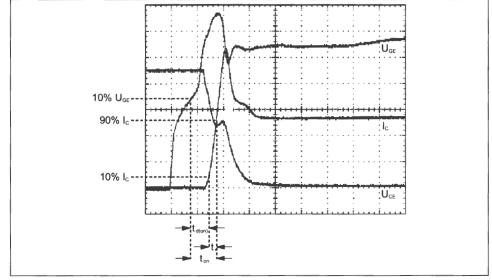

### 3.2.2.1 Einschalten

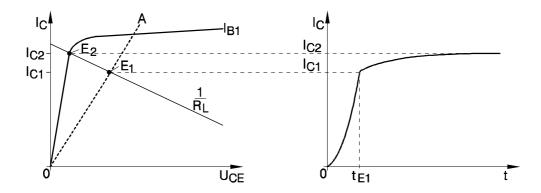

In einem *ohmschen Lastkreis* durchläuft der Arbeitspunkt beim Einschalten mit einem Basisstrom  $I_{B1}$  das Kennlinienfeld entlang der Widerstandsgeraden und verläßt im Schnittpunkt mit der Kurve A, Punkt  $E_1$ , den aktiven Bereich. Zu diesem Zeitpunkt  $(t_{E1})$  hat der Kollektorstrom nahezu seinen Endwert erreicht. Die Zeit  $(t_{E1})$  entspricht damit der *Summe* aus *Verzugszeit*  $t_d$  und *Anstiegszeit*  $t_r$  und ist andererseits verbunden mit dem Aufbau der *Steuerladung*  $Q_B$ . Diese Ladung wird der Basis über den Strom  $I_{B1}$  in der Zeit  $(t_{E1})$  zugeführt. *Vernachlässigt* man zur Abschätzung von  $(t_{E1})$  die *Rekombination* der zugeführten Ladungsträger und ihr *Abströmen* in den *Emitter*, so gewinnt man die Beziehung

$$t_{E1} \approx t_d + t_r = Q_B / I_{B1} \tag{3.6}$$

Weiterhin besteht zwischen *Steuerladung*  $Q_B$  und Kollektorstrom wegen  $Q_B \approx n(0)w_B$  und  $I_C \approx n(0)/w_B$  und ein linearer Zusammenhang von der Form

$$Q_B \approx w_B^2 \cdot I_{C1} \approx w_B^2 \cdot I_C \tag{3.7}$$

Um eine kurze Einschaltzeit zu erzielen, bedarf es eines Transistors mit kleiner Steuerladung. Das erfordert nach Gl. (3.7) eine dünne Basiszone. Mit einer dünnen Basiszone ist allerdings ein großer Schichtwiderstand verbunden. Damit der Querwiderstand der Basis nicht zu groß wird und zu einer ungleichmäßigen lateralen Emitterstromverteilung führt, muß dann gleichzeitig auch die Breite der Basis verkleinert werden.

Ein Meilensteinwar in dieser Beziehung der ab 1985 verfügbare 1000 V SIRET-Transistor [3.3.] Er verfügte über eine Basisdicke von 3  $\mu m$  und eine Emitterbreite von 5  $\mu m$  und erreicht Einschaltzeiten < 30 ns. Das sind Schaltzeiten, wie sie bisher nur mit MOS-Transistoren erzielt werden konnten.

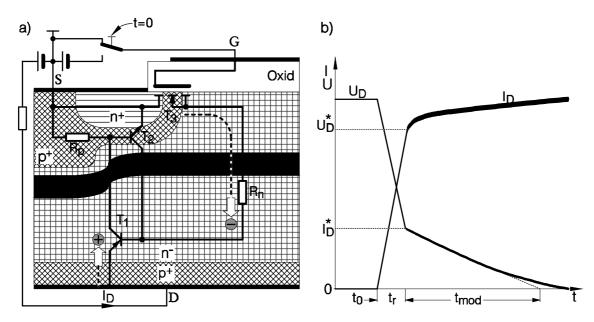

In der Zeitspanne, die der Arbeitspunkt zum Durchlaufen des Quasi-Sättigungsbereiches von  $E_1$  nach E braucht **Bild 3.3**, dient der Basisstrom zum Aufbau der *Sättigungsladungen* in der Basis,  $Q_{BS}$ , und dem Kollektor  $Q_{CS}$ . Im Vergleich zur Steuerladung sind die Sättigungsladungen, insbesondere  $Q_{CS}$  um ein Vielfaches größer. Es dauert daher entsprechend länger, bis der *Speichervorgang* abgeschlossen ist. Während dieser Zeit sinkt die Kollektorspannung in dem Maße, wie der Widerstand der  $\upsilon$ -Zone durch die Überflutung mit Ladungsträgern abnimmt. Der Kollektorstrom steigt daher in diesem 2. Zeitabschnitt,  $t > t_{E1}$  nur noch langsam an.

Bild 3.3: Stromverlauf beim Einschalten: Aufbau der Steuerladung  $(0 \le t \le t_{E1})$ , - der Kollektorladung  $t > t_{E1}$

Einen anderen Verlauf nimmt der *Einschaltvorgang*, wenn in einen *Lastkurzschluß* ( $R_L = 0$ ) geschaltet wird. Es fehlt dann nicht einfach nur der 2. Zeitabschnitt im Kollektorstromverlauf, weil der Arbeitspunkt den aktiven Bereich nicht verläßt. Es kann vielmehr zu einer erheblichen Veränderung der *Feldverteilung* im Kollektor kommen.

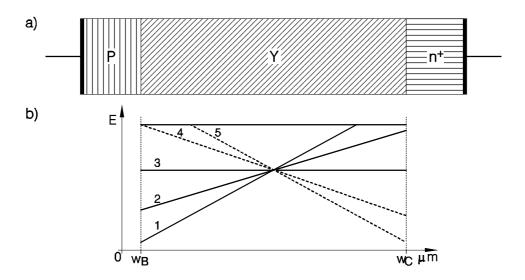

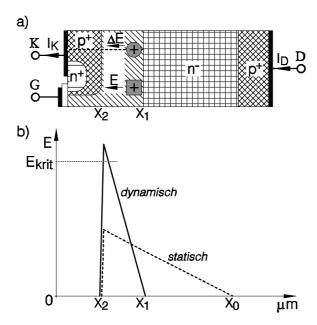

Bild 3.4: Feldstärkeverlauf mit zunehmender Stromstärke

Im stromlosen Zustand möge der Feldstärkeverlauf nach Kurve 1, **Bild 3.4**, vorliegen. Mit Kollektorstrom durchqueren die vom Emitter kommenden Elektronen mit gesättigter Driftgeschwindigkeit  $v_S$  die Raumladungszone. Sie verursachen durch ihre Ladung eine negative Raumladungsdichte der Größe  $-j_C/(Qv_S)$  und kompensieren einen Teil der positiven Donatorladung. Die Nettoladung bestimmt gemäß der Poissongleichung die Steigung der Feldstärke

$$\frac{dE}{dx} = \frac{q}{\varepsilon_0 \cdot \varepsilon_r} \left( N_D - \frac{j_C}{q \cdot v_s} \right) \tag{3.8}$$

wobei  $N_D$ ... Donatorkonzentration [1 / m<sup>3</sup>]

Mit zunehmendem Kollektorstrom wird der Feldverlauf flacher und wird für

$$j_C = j_{C1} = q \cdot N_D \cdot v_s . \tag{3.9}$$

horizontal (Kurve 3, **Bild 3.4**). Nimmt der Kollektorstrom weiter zu, so kehrt sich die Steigerung um, und die Feldstärke an der pv-Grenze geht schließlich gegen Null. Das tritt bei einem Kollektorstrom  $j_C = j_{C2}$  auf (Kurve 4), für den gilt

$$j_{C2} = 2\varepsilon_0 \cdot \varepsilon_r \cdot v_s \cdot \frac{U_{CE}}{v_c^2} + j_{C1}$$

(3.10)

Oberhalb  $j_{c2}$  entfernt sich die Raumladungszone von der p-Grenze, begleitet von einer Basisaufweitung und zieht sich mit wachsendem Kollektorstrom immer mehr an der n<sup>+</sup>-Grenze zusammen.

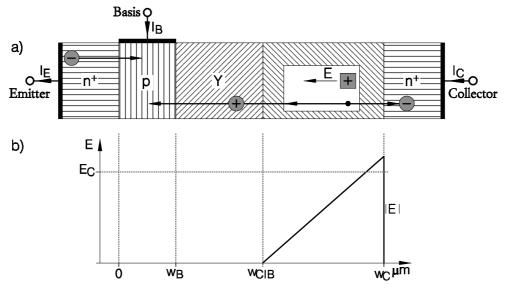

Da die Kollektorspannung für  $R_L=0$  gleich der angelegten Spannung ist, wächst die Spitzenfeldstärke aufgrund der Konstanz der Fläche unter der E(x)-Kurve stark an. Kritisch wird die Situation, wenn die Spitzenfeldstärke den Wert  $E_C$  erreicht, bei dem  $Sto\betaionisation$  einsetzt, **Bild 3.5**. Es werden dann Elektron-Lochpaare generiert. Die Löcher laufen zur p-Basis, steuern den Emitter stärker auf und veranlassen ihn, mehr Elektronen zu injizieren. Diese Elektronen strömen zur Kollektorsperrschicht und generieren ihrerseits neue Löcher durch Stoßionisation, so daß ein regenerativer Prozeß in Gang gesetzt wird **Bild 3.5**. Den Auslöse-Mechanismus bezeichnet man als  $Avalanche\ Injektion$ . Einmal eingeleitet, kann es zu einem lawinenartigen Anwachsen des Kollektorstromes und zu einer Zerstörung des Transistors innerhalb von Bruchteilen einer Mikrosekunde kommen. Dies wird bei Hochvolttransistoren als Hauptursache für das Auftreten des  $Zweiten\ Durchbruchs$  angesehen **Bild 3.6**.

Bild 3.5: Avalanche Injektion: a) Schichtenfolge und Elektron-Loch- Paar Generation b) Feldstärkeverlauf mit  $E_C$  = kritische Feldstärke

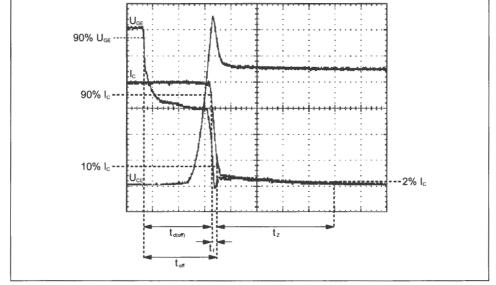

#### 3.2.2.2 Abschalten

Beim Abschalten des Transistors mit negativem Basisstrom  $I_{BR}$  fließt der Kollektorstrom in voller Höhe weiter, solange sich die Klemmenspannung  $U_{CE}$  nicht erhöht. Und das ist solange der Fall, wie im ..-Kollektor noch Ladungsträger gespeichert sind. Erst nach *Abbau* der *Sättigungsladung*, am Ende der sog. Speicherzeit  $t_S$ , fällt der Kollektorstrom ab. Bei Vernachlässigung der Rekombination entspricht  $t_S$  der Zeitspanne, die der Basisstrom braucht, um die Sättigungsladung  $Q_{RS} + Q_{CS}$  abzuführen,

$$t_{s} = \frac{Q_{BS} + Q_{CS}}{I_{BR}} \tag{3.11}$$

Mit hinreichend großem Basisstrom sollte sich daher die Speicherzeit beliebig verkürzen lassen. Das stimmt nur bis zu einem gewissen Grad. Denn mit der Höhe des Basisstromes ändert sich der Charakter des Trägerabbaus.

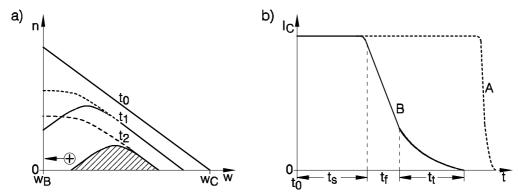

Um dies zu verdeutlichen, sind in **Bild 3.6**a die Trägerprofile für  $I_{BR} < I^*$  und  $I_{BR} > I^*$  skizziert. Der für die Unterscheidung maßgebende Strom I\* hängt vom Verhältnis der Trägerbeweglichkeiten,  $b = \mu_n/\mu_p$  ab und ist gegeben durch  $I^* = I_C/(b+1)$ .

Für  $I_{BR} < I^*$  bleibt die Steigung des Trägerprofiles an der  $p\upsilon$ -Grenze negativ. Der  $p\upsilon$ -Übergang übernimmt Spannung, sobald der Randwert  $n(w_Bt)$  der Überschußträger Null wird. Im gleichen Moment geht auch die Speicherladung  $Q_{CS}$  gegen Null. Im Falle

Bild 3.6: Ausschalten des Transistors mit Basisstrom  $I_{BR}$ a) Trägerprofile b)Basisstromverläufe

$I_{BR} > I^*$  wird die Steigung des Trägerprofiles bei  $x = w_B$  positiv und der Randwert  $n(w_B, t)$  sinkt schneller als die Trägerdichte im Inneren der v-Zone. Der pv-Übergang nimmt auch hier Spannung auf, sobald der Randwert Null wird. *In diesem Fall* sind aber noch *Ladungsträger im* v-*Gebiet gespeichert*. Sie *diffundieren* in die Raumladungszone und liefern somit einen merklichen *Strombeitrag* während der Spannungsaufnahme und auch noch danach. Dabei entsteht dann ein Ausläufer, den man als *Tailstrom* bezeichnet. **Bild 3.6** b zeigt die charakteristischen Unterschiede im Stromverlauf. Beim Abschalten mit *großem Basisstrom* (Kurve B) ist die *Speicherzeit kürzer*, die *Fallzeit* aber *länger* als beim Abschalten mit kleinem Basisstrom und außerdem kann ein Tailstrom auftreten.

Ferner macht sich für  $I_{RR} > I^*$  ein anderer Effekt störend bemerkbar. Beim Vorwandern der

Raumladungszone werden Löcher aus dem  $\upsilon$ -Gebiet extrahiert und zur p-Basis transportiert. Sie durchlaufen dabei die Raumladungszone mit gesättigter Driftgeschwindigkeit und vergrößern durch ihre Ladung die positive Raumladungsdichte. Das führt zu einem Anstieg der Spitzenfeldstärke an der  $p\upsilon$ -Grenze. Zu einer ausgeprägten Feldüberhöhung kommt es dann, wenn die Kollektorspannung schnell ansteigt, während der Kollektorstrom noch seine volle Höhe hat. Solche Verhältnisse stellen sich im Falle einer induktiven Last ein. Kritisch wird es, wenn die Feldstärke so groß wird, daß Stoßionisation einsetzt. Die generierten Löcher strömen zur Basis und erzeugen auf ihrem Weg zum Kontakt am Querwiderstand der Basis einen zusätzlichen Spannungsabfall, durch den der Emitter im Zentrum der Emitterfläche stärker in Flußrichtung gepolt wird.

Das ruft eine *Lawinen-Injektion* hervor, die *lokal begrenzt* ist und *Stromfilamente* verursacht. Die Folge ist das Auftreten thermischer Instabilitäten und die Gefahr der Zerstörung des Transistors.

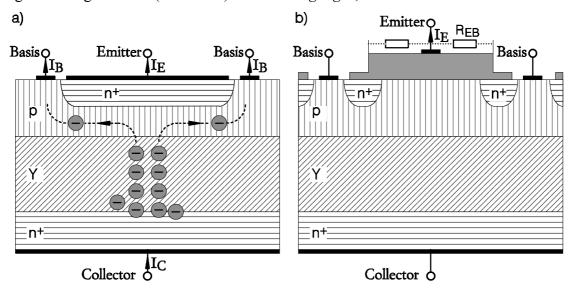

# 3.2.2.3 Stromeinschnürung

In konventionellen Transistoren bewirkt der Querwiderstand der Basis beim Abschalten eine Stromverdrängung zur Mitte der Emitterfläche Bild 3.7. Unter dem Emitter kann erst dann ein lateraler Basisstrom fließen, wenn die Emitter-Basis-Grenze ein Potentialgefälle aufweist. Dazu muß zuvor die Speicherladung im Randbereich abgeführt werden. Der Abbau der Speicherladung beginnt daher im Randbereich des Emitters und pflanzt sich ver-

zögert zum Inneren fort. Der Kollektorstrom bleibt dabei konstant und schnürt sich schließlich in einen Kanal von der Breite einer Diffusionslänge ein. Auf diese Weise entsteht vor Beginn des eigentlichen (vertikalen) Abschaltvorganges, wie er zuvor betrachtet worden ist,

Bild 3.7: a) Stromeinschnürung beim Ausschalten

b) Transistor mit Zellenstruktur und Emitter-Ballastwiderständen

eine hohe Stromdichte mit Werten von 100 - 1000 A/cm<sup>2</sup>. Diese Stromdichte ist von der Größenordnung der kritischen Stromdichte  $j_{C2}$ , Gl. (3.10), und kann beim Abschalten gegen eine hohe Kollektorspannung zum Auslösen des Zweiten Durchbruchs führen.

# 3.2.3 Maßnahmen gegen den Zweiten Durchbruch

Als wirksame Gegenmaßnahme wird in heutigen Transistoren die Emitterfläche in so feine Zellen unterteilt, **Bild 3.7**b, daß ein lateral homogenes Abschalten gewährleistet ist. Zusätzlich wird durch Widerstände in den Emitter-Kontakten die gleichmäßige Stromverteilung auf die einzelnen Zellen erzwungen. Es wird damit erreicht, daß bei einer Begrenzung des Durchlaßstromes auf  $j_c \ll j_{c2}$  der auslösende Mechanismus für den Zweiten Durchbruch

*nicht mehr* die *Feldüberhöhung* an der  $\upsilon n^+$ -Grenze ist. Die Feldüberhöhung im  $p\upsilon$ -Übergang läßt sich ebenfalls ausschalten, in dem die Stromdichte auf Werte  $< j_{C1}$  begrenzt wird.

Das ist bei 1000 V-Transistoren mit  $j_{C1} \approx 200~{\rm A/cm}^2$  ohnehin erforderlich wegen des  $h_{Fe}$ -Abfalls mit  $j_C$ . Die beweglichen Ladungsträger haben in diesem Fall keinen Einfluß mehr auf das Feld. Der Transistor kann damit praktisch gegen die Kollektor-Basis-Durchbruchspannung  $U_{CB0}$  abgeschaltet werden. Das bedeutet eine erhebliche Verbesserung des sicheren Arbeitsbereiches. Die Experimente zeigen darüber hinaus, daß bei diesen Transistoren auf die RC-Beschaltung verzichtet werden kann.

# 3.3 Hochsperrfähige-MOSFETs Technologie

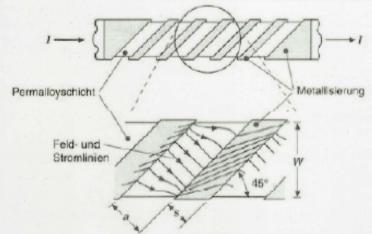

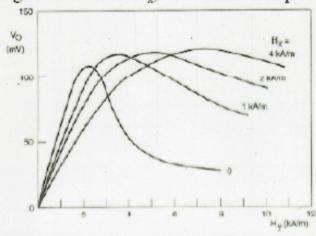

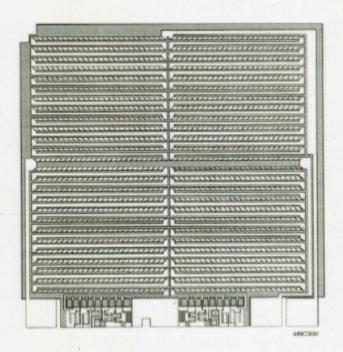

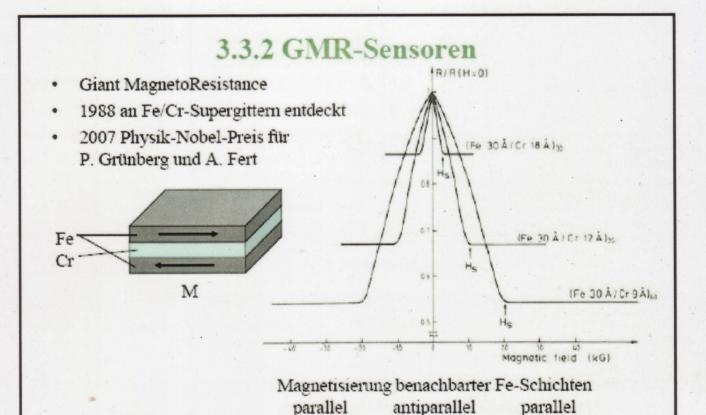

## 3.3.1 Zusammenfassung

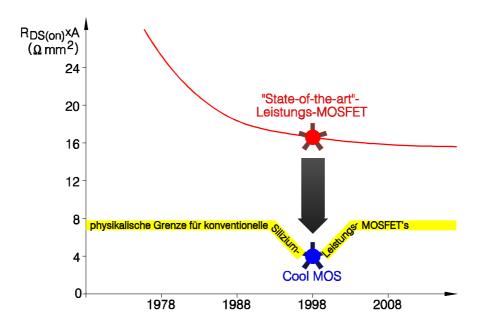

Hochvolt-Transistoren (400 bis 1000 V) erreichten Ende der 80er Jahre mit der bekannten MOS-Struktur eine Entwicklungsgrenze. Verbesserungen des Einschaltwiderstands ließen sich im Prinzip nur durch die Maximierung der in die tradionellen Gehäuse montierbaren Siliziumfläche erzielen. Bei den Hochvolt-MOSFET-Familien (600 bis 1000 V) beispielsweise,,CoolMOS" von Siemens dagegen ist der R<sub>DS(on)</sub> um den Faktor 5 bis 10 bei gleicher Chipfläche reduziert.

Leistungs-MOSFETs zählen seit nunmehr 20 Jahren zu den bedeutendsten Komponenten in der Leistungselektronik. Mit einem Marktvolumen von 1,4 Mrd. Dollar in 1997 und einem prognostizierten jährlichen Wachstum von 15 % bis ins Jahr 2001 wird die Bedeutung dieser Bauelemente auch in Zukunft weiter zunehmen.

Im Niedervoltbereich (Sperrspannungen  $\leq 100\,V$  wurde in den letzten Jahren eine Vielzahl neuer Technologien vorgestellt, die auf dem FZ-Markt zu den Technologien eingeführt, die extrem niedrige Einschaltwiderstände zurealisiern erlaubt (z.B.  $R_{DS(\text{on})} < 6m\Omega$ , bei  $U_{DS} = 30\,\text{V}$ ), was auch kleinere Gehäuseformen erlaubt.

Bei den Hochvolt-Transistoren (400 bis 1000 V) war Ende der 80er Jahre mit der bekannten MOS-Struktur eine Entwicklungsgrenze erreicht. Verbesserungen des Einschaltwiderstandes konnten - mangels technologischer Verbesserungspotentiale - häufig nur durch Maximierung der in die traditionellen Gehäuse, wie TO-220 oder D-Pak, montierbaren Siliziumfläche erzielt werden.

Kürzlich wurde eine neue Hochvolt-MOSFET-Familie (600 bis 1000 V) unter der Bezeichnung CoolMOS vorgestellt. Dahinter verbirgt sich eine revolutionäre MOS-Technologie, die im Vergleich zu bekannten Technologien eine Reduzierung des  $R_{DS(on)}$  um den Faktor 5 bis 10 bei gleicher Chipfläche ermöglicht.

Die Erhöhung der Leistungsdichte mit dem Ziel der Miniaturisierung und der Systemintegration ist eine der wesentlichen Herausforderungen für zukünftige leistungselektronische Systeme. Darüber hinaus werden sich auch die Anforderungen bezüglich eines hohen Systemwirkungsgrades über den gesamten Lastbereich, bezüglich der Regeldynamik auf Störgrößen, der Zuverlässigkeit etc. weiter verschärfen. Wesentliche Impulsgeber für diese Weiterentwicklungwaren bisher und sind auch weiterhin die Leistungshalbleiterbauelemente.

In der Vergangenheit sind Versuche, leistungselektronischer Systeme wie Schaltnetzteile oder Umrichter deutlich kleiner zu bauen, vielfach an den dazu notwendigen Bauelementen gescheitert. Eine zentrale Komponente bilden dabei die Leistungshalbleiterschalter, die für Systeme am 240/400-V-Netz Sperrspannungen von 600 V, 800 V oder 1000 V - je nach Schaltungstopologie - verkraften müssen.

In der zweiten Hälfte der 70er Jahre gelang hier der bisher entscheidendste Schritt in eine neue Bauelemente-Generation: Die Entwicklung der Leistungs-MOSFETs, die rasch zu einer nahezu vollständigen Ablösung der Bipolar-Transistoren in der Leistungselektronik führten. Mit den Leistungs-MOSFETs wurde der Schritt zur direkten Verbindung der

Mikroelektronik und der Leistungselektronik vollzogen - sowohl fertigungstechnisch (MOS-Prozeßtechnik) als auch aus Anwendersicht ("leistungslose Ansteuerung" etc.). Die Weiterentwicklung der Leistungs-MOSFETs wird vom Trend zur Miniaturisierung und Wirkungsgraderhöhung leistungselektronischer Systeme getragen.

Im Vordergrund dieser Entwicklung stehen die Reduktion des Einschaltwiderstandes  $R_{DS(on)}$  die Steigerung der Robustheit bezüglich kritischer Schaltzustände, die Avalanche-Festigkeit sowie die Absenkung der benötigten Treiberleistung durch Verringerung der Gate-Ladung. Diese Hochvolt-MOSFET-Familien sollen hier weitere Maßstäbe hinsichtlich Einschaltwiderstand, Schaltfrequenz, Steuerleistung und dynamische Verluste setzen.

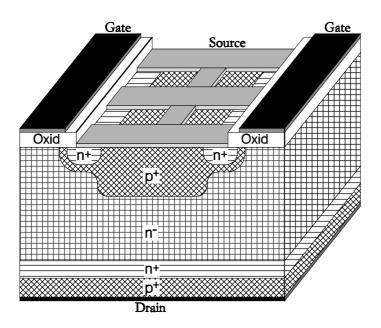

# 3.4 MOS-gesteuerte Hochvolt-Transistoren

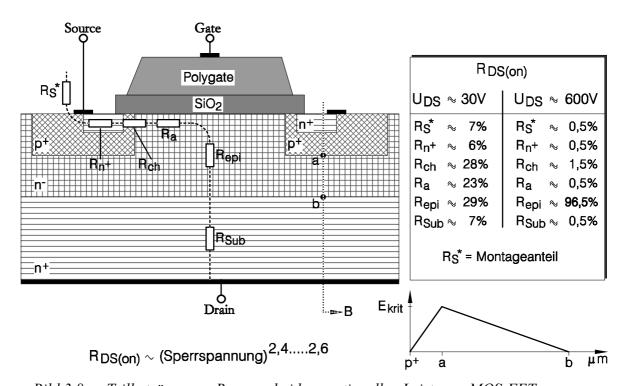

Bild 3.8: Teilbeträge zum  $R_{DS(on)}$  bei konventionellen Leistungs-MOS-FETs: Zellenstruktur mit den Teilwiderständen sowie deren Aufteilung bei Hochund Niedervolt-MOSFETs (oben); Feldstärkeverlauf innerhalb der Epitaxieschicht (unten)

Bild 3.8 zeigt die Zelle eines konventionellen Leistungs-MOSFETs mit den wichtigsten Teilbeiträgen zum Einschaltwiderstand  $R_{\rm DS(on)}$ . Der Einschaltwiderstand wird bei Hochvolt-MOS-Transistoren mit Durchbruchspannungen über 300 V in erster Linie durch die Dotierung und die Dicke des Epitaxie-Gebietes bestimmt und nur geringfügig durch die Zellengeometrie und das Substrat-Gebiet. Daher ist - im Gegensatz zu Niedervolt-MOS-FETs mit Sperrspannungen kleiner 100 V - eine Reduzierung des  $R_{\rm DS(on)}$  nur in sehr beschränktem Maße durch die Optimierung der Zellengeometrie möglich. Das Hauptaugenmerk zur Verbesserung der Leistungsfähigkeit eines Hochvolt-MOSFETs muß sich auf eine Reduzierung des Epitaxie- oder Driftzonen-Widerstandes richten. Maßgebend für diesen

Widerstand ist die Dicke und Dotierung der Driftzone - beide Größen legen zugleich aber auch die Sperrfähigkeit des Transistors fest. Um die Sperrspannung zu erhöhen, muß die Dotierung reduziert und zugleich die Schichtdicke vergrößert werden. Damit steigt der Widerstand des Transistors als Funktion seiner Sperrfähigkeit mehr als quadratisch an. Für Anwendungen, die hochsperrende Transistoren erfordern, bedeutet dies einen hohen Chipflächenbedarf und damit hohe Kosten, hohes Volumen, hohe Ansteuerleistung usw.. Aus diesem Grund gab es in der Vergangenheit bereits intensive Bemühungen zur Verbesserung der Durchlaßeigenschaften eines MOSFETs. Der bislang erfolgreichste Ansatz zur Lösung dieses Problems war der "Insulated-Gate Bipolar-Transistor" IGBT (Bild 3.9)

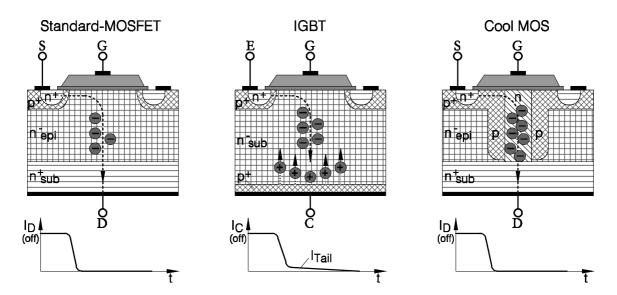

Bild 3.9: Schematischer Querschnitt durch einen konventionellen MOSFET, einen IGBT und den neuen CooLMOS-Hochvolt-MOSFET von Siemens mit vertikalen p-Streifen

# IGBT - mehr Ladungsträger aber auch höhere Ausschaltverluste

Beim IGBT wird im eingeschalteten Zustand die Konzentration der für den Stromtransport zur Verfügung stehenden Ladungsträger durch die Injektion zusätzlicher Träger aus der rückseitigen p-Schicht stark erhöht. Da diese Träger sich mit den engegengesetzt geladenen Elektronen aus dem Kanalstrom genau die Waage halten, kann die gesamte Ladungsträger-Konzentration um mehrere Größenordnungen über der Grunddotierung liegen. Somit wird die Leitfähigkeit der Driftzone entscheidend verbessert - man spricht von einer Überschwemmung dieser Zone. Diese effektive Art der Widerstands-Reduzierung wird allerdings auch mit Nachteilen erkauft:

Wird der Transistor abgeschaltet, so müssen die zusätzlich eingebrachten Ladungsträger wieder aus der Driftzone entfernt werden. Dies verursacht den charakteristischen "Tail-Strom" von IGBTs und damit erhöhte Ausschaltverluste. Zudem führt die rückseitige p-Schicht zu einer "Serien-Diode" im Laststromkreis, so daß die für viele Anwendungen vorteilhafte Rückwärts-Leitfähigkeit eines MOSFETs (intrinsische Inversdiode) wegfällt. Des weiteren limitiert die Restspannung  $U_{ce.\ sat}$  die erreichbare minimale Verlustleistung.

# 3.5 Eigenschaften von Leistungstransistoren mit vertikalen p-Streifen (Cool Mos)

#### 3.5.1 Durchlaßverhalten

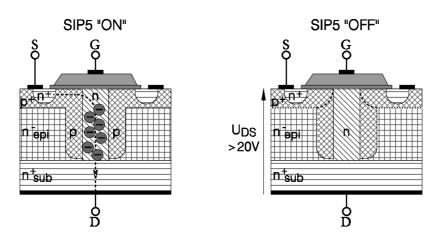

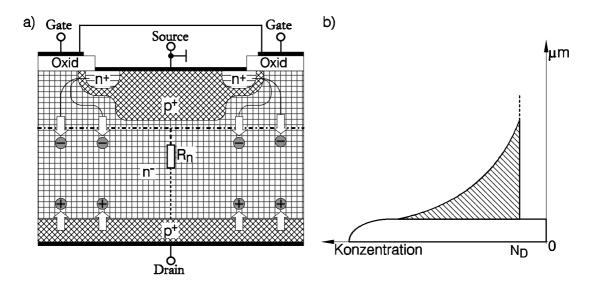

Bild 3.10: Funktionsprinzip eines CoolMOS-Transistors. Eine sich über die gesamte Epi-Schicht erstreckende Raumladungszone ermöglicht die hohe Sperrfähigkeit im ausgeschalteten Zustand

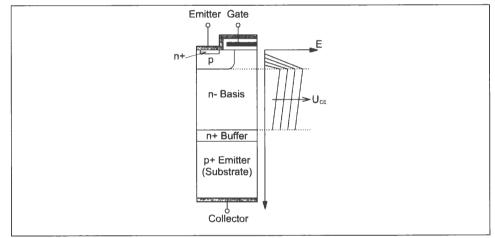

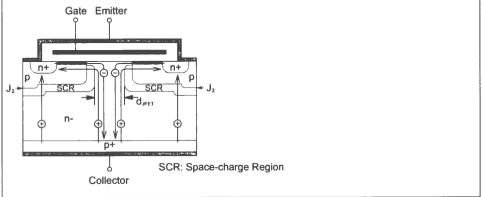

Einen völlig anderen Weg zur Reduzierung des Driftstrecken-Widerstandes beschreitet das "SIP5"-Konzept der Siemens-CoolMOS-Transistoren. Dieses Konzept stützt sich zunächst auf das herkömmliche MOSFET-Prinzip. Im Gegensatz dazu werden jedoch in die Driftzone vertikale p-Streifen eingebaut (**Bild 3.10**). Diese Technik ermöglicht infolge der feinstrukturierten Folge von Schichten entgegengesetzter Dotierungen eine deutliche Erhöhung der Dotierung der Driftzone. Damit wird bereits bei 600-V-Transistoren der spezifische Widerstand gegenüber dem Stand der Technik um den Faktor 5 reduziert.

Mit steigender Drain-Source-Spannung breitet sich die Raumladungszone an der Grenzschicht zwischen den p- und n-Streifen immer weiter aus, was schließlich zu einer völligen Ausräumung der Epi-Schicht führt. Die Sperrspannung wird also nicht nur wie bisher in vertikaler Richtung, sondern auch in horizontaler Richtung aufgebaut.

Zur Erzielung höherer Sperrspannung muß lediglich der Bereich mit den p-Streifen verlängert werden; eine Absenkung der Dotierung wie bei herkömmlichen Transistoren ist nicht mehr erforderlich.

Damit ergibt sich der im **Bild 3.11** dargestellte lineare Zusammenhang zwischen dem spezifischen Widerstand und der maximalen Sperrfähigkeit des Transistors. Entsprechend wachsen die Vorteile der neuen Technologie mit der Sperrspannung - bei 1000-V-MOSFETs erreicht die SIP5-Technologie Verbesserungen von mehr als einer Zenerpotenz.

Das Schaltverhalten dieser Transistoren entspricht dem konventioneller MOSFETs, im Gegensatz zu IGBTs tritt kein Tailstrom auf. Vielmehr reduziert sich aufgrund der nun möglichen Verringerung der Chipfläche auch die Gate-Ladung und damit die erforderliche Ansteuerleistung des Transistors.

Mit o.g. Technologie wird nicht nur eine Verbesserung gegenüber den bisherigen Technolo-

gien erreicht, sogar der bisher als physikalisches Limit für Silizium-MOSFETs angesehe

Bild 3.11: Flächenspezifischer  $R_{DS(0n)}$  in Abhängigkeit von der Sperrspannung bei konventionellen MOSFETs und den neuen Cool-MOS-Transistoren

nen flächenspezifischen Widerstand (s. Bild 3.12).

Bild 3.12: Entwicklung des flächenspezifischen Widerstandes bei 600 V Leistungs-MOSFETs.

Einige Schlagwerte für die Nutzung dieser MOSFET-Technologie sind:

- niedrige Komponentenkosten,

- geringerer Montageaufwand,

- drastische System-Miniaturisierung

- höhere Schaltfrequenzen,

- weniger parasitäre Netzwerkkomponenten durch kompakteren Aufbau,

- geringer Ansteueraufwand und niedrigere Verluste.

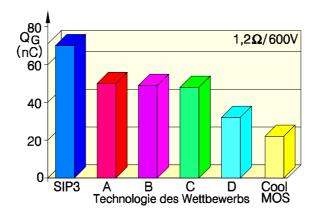

## 3.5.2 Reduzierte Kapazitäten, optimiertes Schaltverhalten

Durch das neue Zellendesign mit den charakteristischen p-Säulen wurden auch die FET-Kapazitäten neu definiert. Als Resultat der enormen Chipflächen-Reduktion weisen Cool-MOS-Transistoren eine sehr niedrige Eingangskapazität verglichen mit  $R_{DS(\ on)}$  gleichen Transistoren in konventioneller Technologie auf. Damit wird auch die zum Laden der spannungsabhängigen Eingangskapazität erforderliche Gateladung sehr klein. Die Gateladung  $Q_G$  wiederum ist ein Maß für die bei einer bestimmten Schaltfrequenz  $f_{\rm sw}$  erforderliche Ansteuerleistung  $P_G$ :

$$P_G = Q_G \cdot U_{GS} \cdot f_{sw} \tag{3.12}$$

Da in vielen Anwendungen die Leistungs-MOSFETs ohne diskrete Treiberstufe direkt aus Ansteuer-ICs (z.B. PWM-ICs) betrieben werden sollen, schlägt sich die erforderliche Treiberleistung unmittelbar in den IC-Kosten nieder. Umgekehrt steigt bei gegebenem Ansteuer-IC die Schaltfrequenz mit kleiner werdender Gateladung des Transistors.

Bild 3.13: Vergleich der Gateladung von Mitbewerber-Technologien mit der des CoolMOS.

**Bild 3.13** zeigt einen auf ein fiktives  $1,2\Omega$ -Bauelement skalierten Gateladungs-Vergleich der wichtigsten auf dem Markt erhältlichen Hochvolt-MOSFET-Technologien. Deutlich ist die drastische Verringerung der Gateladung bei der neuen CoolMOS-SIP5-Technologie zu erkennen. Damit sind diese Transistoren mit der niedrigsten Steuerleistung, der billigsten Ansteuerschaltung und den höchsten Schaltfrequenzen zu betreiben.

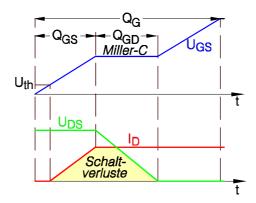

Bild 3.14: Zeitlicher Kurvenverlauf der Gate-Source-Spannung, Drain-Source Spannung und des Drainstroms während des Einschaltvorganges

Im **Bild 3.14** sind die idealisierten Schaltkurven beim Einschalten eines MOSFETs dargestellt. Die Schaltverluste entstehen im wesentlichen während der Überlappungsphase von Strom und Spannung beim Schaltvorgang - beim Einschalten unter Spannung aber auch durch das Entladen der MOSFET-eigenen Ausgangskapazität. Der zeitliche Verlauf des Abfalls bzw. Anstiegs der Drain-Source-Spannung während des Schaltvorgangs - und damit die Schaltverluste - werden vom Umladevorgang der Gate-Drain-Rückkopplungskapazität ("Miller"-Kapazität) bestimmt. Je niedriger die Gateladung und dabei besonders  $Q_{GD}$ . desto geringer sind die Schaltverluste.

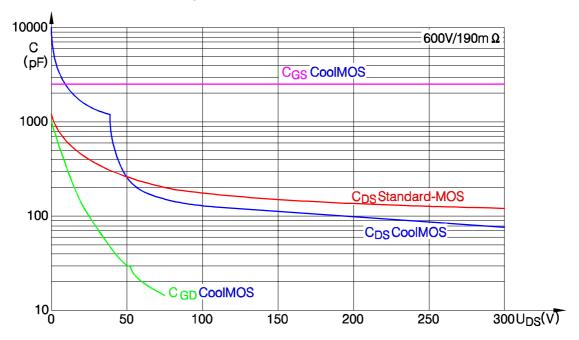

Die Ausgangskapazität wird im wesentlichen durch die Drain-Source-Kapazität bestimmt; diese hängt von der Mantelfläche der p-Inseln ab. Da die Mantelfläche im Vergleich zu den bei konventionellen Leistungs-MOSFET dominierenden p+-Inseln groß ist, wird die Ausgangskapazität bei kleinen  $U_{DS}$ -Spannungswerten sehr groß (s. **Bild 3.15**).

Bild 3.15: CoolMOS reduziert die MOSFET-Kapazitäten im Vergleich zu Standard-MOSFETs.

Dies wirkt bei harten Ausschaltvorgängen schaltentlastend. Von großer Bedeutung für den Einsatz bei hohen Schaltfrequenzen ist nun aber, daß die in der Ausgangskapazität gespeicherte Energie  $E_{\rm DS}$  bei Hochvolt-Anwendungen  $(U_{D\ddot{S}max}>200\,V)$  niedriger liegt als im Fall  $R_{\rm DS(on)}$ -gleicher Transistoren in Standarf-MOSFET-Technologie:

$$E_{DS} = \int_{0}^{U_{D\dot{S}.max}} C_{DS}(U) \cdot U \cdot dU \tag{3.13}$$

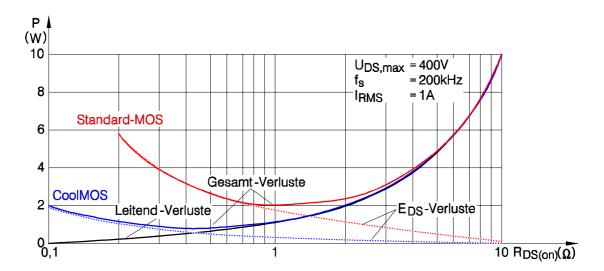

Diese Energie, die bei jedem Einschaltvorgang im Transistor in Wärme umgesetzt wird, steigt mit der Chipfläche an und begrenzt damit die minimal errreichbare Verlustleistung (**Bild 3.16**). Durch das optimierte Produkt aus  $R_{DS(on)}$  und  $E_{DS}$  sowie durch seine niedrigen Eingangskapazitäten ist der CoolMOS sowohl bei niedrigen als auch bei hohen Schaltfrequenzen dem herkömmlichen Leistungs-MOS-Transistor überlegen.

Bild 3.16: Geringere Gesamtverluste durch verbessertes Produkt von  $R_{DS(on)}$  und  $E_{DS}$

Das Ausgangskennlinienfeld eines CoolMOS entspricht dem eines Standard-MOSFETs mit dem charakteristischen linearen Verlauf bei niedrigen  $U_{DS}$ -Werten - ohne die für IGBT und Bipolartransistoren typische Dioden-Anlaufschwelle. Das Termperaturverhalten  $R_{DS(on)}$  entspricht dem von Standard-MOSFETs.

Aufgrund eines inneren Streifenaufbaus (Bild 4.3) weist der CoolMOS-Transistor bei der Kommutierung der Inversdiode eine im Vergleich zu konventionellen MOSFETs höhere Rückstromspitze auf, die wie bei allen Leistungs-MOSFETs relative scharf abreißt. Die entstehende Verlustenergie wird nahezu ausschließlich im einschaltenden Transistor dissipiert, wobei - aufgrund seiner sehr kleinen Reserve-recovery-Ladung  $Q_{rr}$  - der CoolMOS insgesamt eine Reduktion der dynamischen Verluste erlaubt.

Zur Verbesserung des Störabstandes bei Brückenanwendungen wurde die Gate-Source-Einsatz-Spannung auf typisch 4,5 V (Fenster 3,5 bis 5,5 V bei 25°C) angehoben. Aufgrund

ihrer hohen Steilheit erreichen die CoolMOS-Transistoren trotzdem bereits bei 10 V Gatespannung ihren nominalen R<sub>DS(on)</sub>.

## 3.5.3 Robustheit nahe an physikalischer Grenze

Robustheit umfaßt im wesentlichen die Kriterien Avalanche-, dU/dt- und Kurzschluß-Festigkeit, aber auch die Qualität des Gate-Oxids. Avalanche-feste Transistoren reduzieren den zur Beherrschung von Überspannungen erforderlichen Sperrspannungs-Sicherheitsabstand, wodurch sich in vielen Anwendungen vergleichsweise niedersperrende Transistoren einsetzen lassen, die bei gleichem R<sub>DS(on)</sub> weniger Chipfläche beanspruchen und damit kostengünstiger sind. Bei den konventionellen Hochvolt-MOSFETs spielt dies eine entscheidende Rolle, weil der R<sub>DS(on)</sub> dieser Transistoren überproportional mit der Durchbruchspannung ansteigt. So liegt bei konventioneller Technologie der Widerstand eines 800-V-Transistors um den Faktor 2 über dem eines flächengleichen 600-V-Transistors, während er in der neuen CoolMOS-Technologie infolge des linearen Zusammenhangs nur um 30 % ansteigt. Dies ist ein gravierender Vorteil in der Anwendung höhersperrender Leistungs-MOSFETs. Damit ist die Frage zu klären, ob nicht ein höhersperrender Leistungs-MOSFET, der nicht im Avalanche-Bereich betrieben wird, bezüglich der Gesamt-Verlustleistungs-Bilanz Vorteile hat. Es darf nicht vergessen werden, daß die Verlustleistung durch die im Avalanche-Betrieb zusätzlich im Transistor umgesetzte Energie bei hohen Schaltfrequenzen rasch ansteigen kann.

Beim CoolMOS wurden die Erkenntnisse aus der Avalanche-festen S-FET-Technologie (1) angewandt, so daß dU/dt-Festigkeit spezifiziert werden kann. Die im Transistor umsetzbare Energie hängt nur noch vom Siliziumvolumen und nicht mehr von parasitären Einflußparametern ab, da ein Einschalten des parasitären Bipolartransistors unter allen Betriebszuständen vermieden wird.

Generell gilt, daß die Gesamtverluste - inklusive der Avalanche-Verluste - in einem Rahmen bleiben müssen, bei dem die maximal zulässige "Junction"-Temperatur des Transistors nicht überschritten wird. Vergleicht man die absoluten Avalanche-Energiewerte, so liegen diese - infolge des drastischen Chipflächen-"Shrinks" - bei CoolMOS-Transistoren teilweise niederiger als bei  $R_{DS(on)}$ -gleichen Hochvolt-MOSFETs in Standard-Technologie.

Bei Kurzschlußtests an einem Zwischenkreis mit sehr niedriger Impedanz und 350 V Zwischenkreisspannung begrenzt der CoolMOS den Kurzschlußstrom nach dem Einschaltenentsprechend seiner Ausgangskennlinie. Die am Transistor anstehende volle Zwischenkreisspannung und der Kurzschlußstrom führen dabei zu einer hohen Verlustleistung im Chip. Über eine schnelle Kurzschlußerkennung (z.B.  $U_{DS}$ -Überwachung) ist jedoch eine gefahrlose Abschaltung des CoolMOS unddamit die Beherrschung des Kurzschlusses möglich.

#### 3.5.4 Einfacher Aufbau von Netzteilen

Mit CoolMOS-Transistoren wird es möglich, Netzteile mit bis zu 5 kW Ausgangsleistung unter Verwendung von nur vier Schaltern im TO-220-Gehäuse zu realisieren, wofür bislang Vollbrücken mit Schalter im TO-264-Gehäuse bzw. Module erforderlich waren. Bis über 2 kW Ausgangsleistung ist nun sogar der Aufbau des gesamten Systems in SMD-Technik

möglich!

Anwendungsfelder in diesem Leistungsbereich sind Schaltnetzteile für Workstations (Server), unterbrechungsfreie Stromversorgungen (USV), Hochspannungswandler für die Mikrowellen- und Medizintechnik, Induktionsherde, Schweißgeräte usw. Generell gilt, daß CoolMOS-Transistoren konventionelle Power-MOSFETs in allen Anwendungen ersetzen können - in den meisten Fällen sogar ohne jede Schaltungsanpassung.

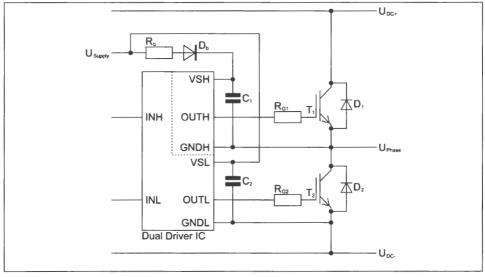

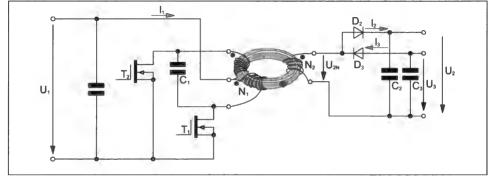

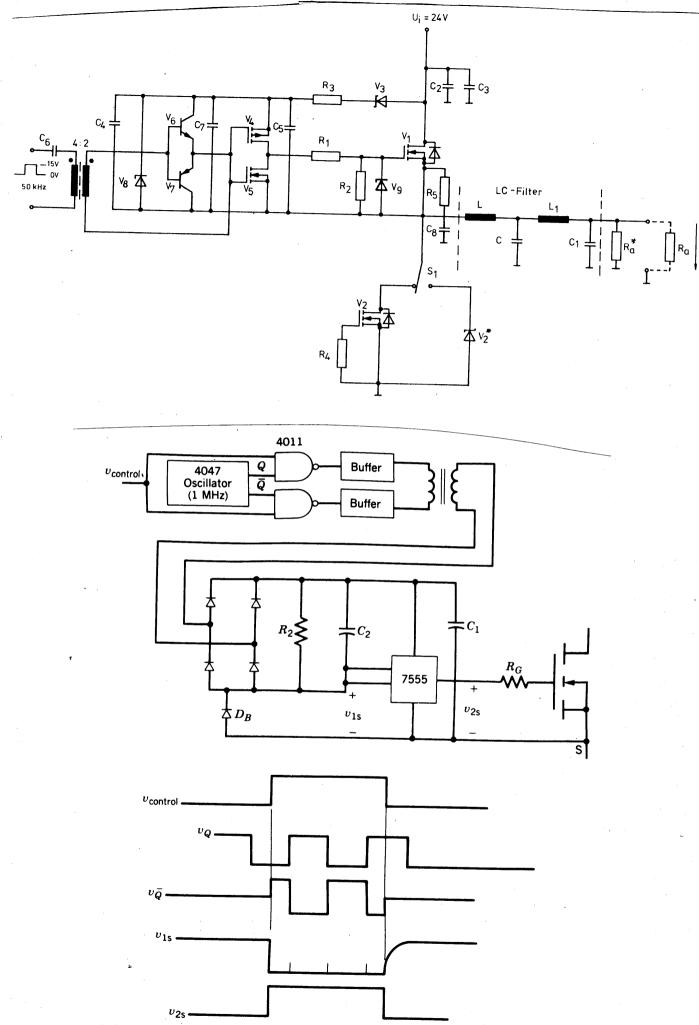

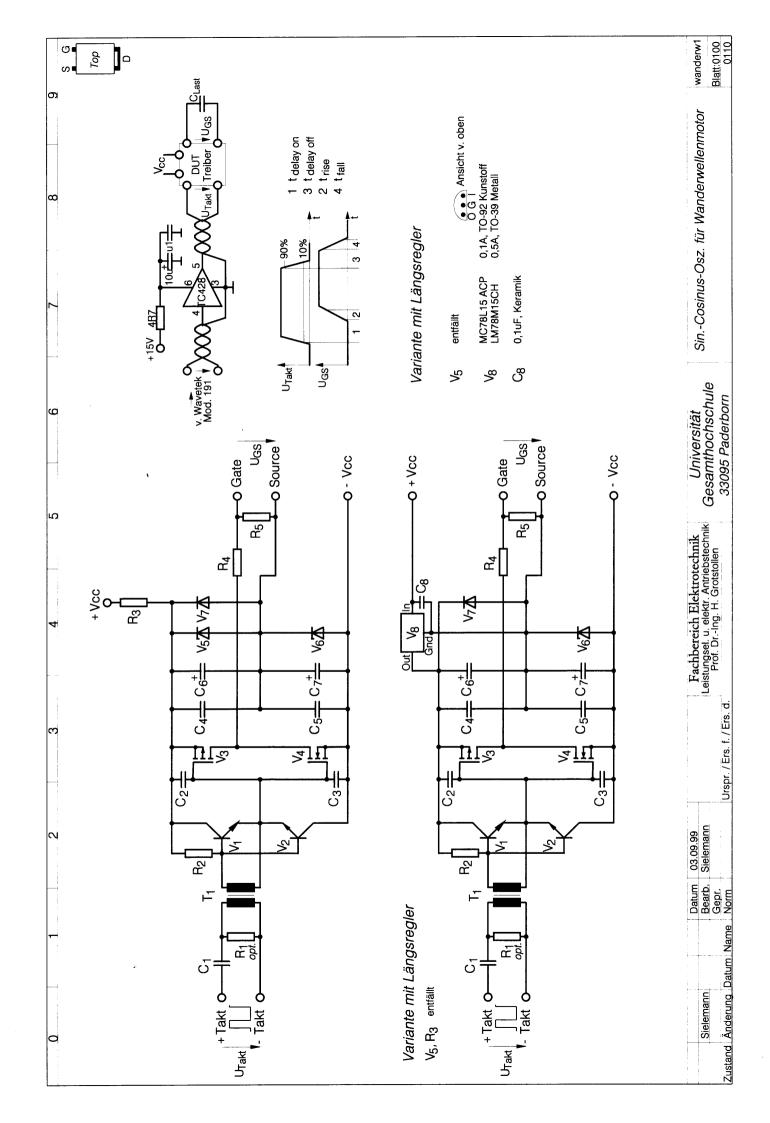

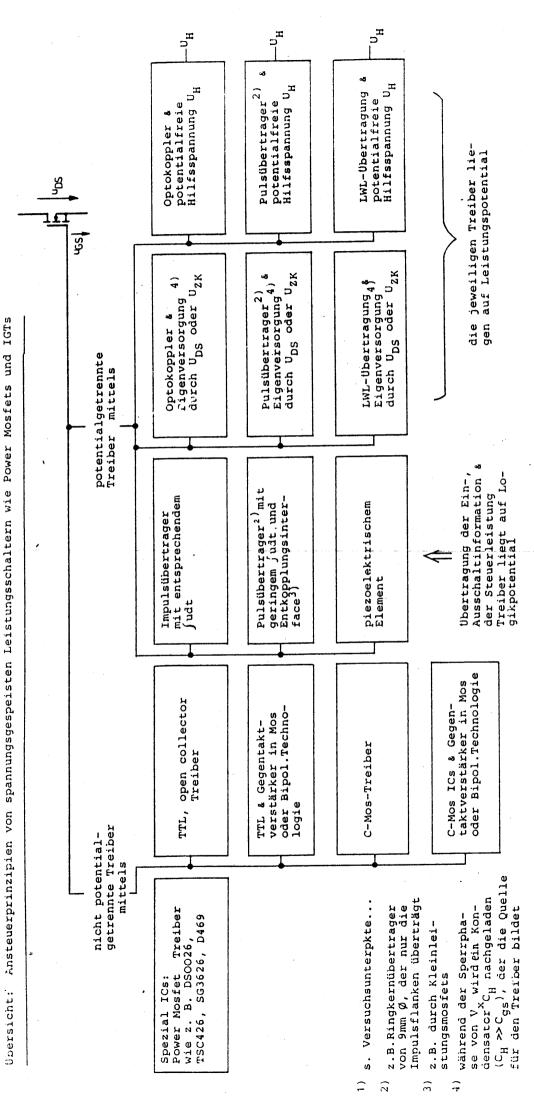

Die Bilder Bild 3.13 und Bild 3.15 zeigen typische Anwendungsfelder für CoolMOS-Transistoren. Dazu zählen neben den klassischen Hoch-/Tief-Setzstellern (vgl. PFC-Leistungsfaktorkorrektur) auch die in nahezu allen Schaltnetzteilen bis 250 W eingesetzten Flußbzw. Sperrwandler sowie im ZVS-Modus (zero-voltage-switching) arbeitende Brückenschaltungen.

Bei Schaltfrequenzen über 100 kHz bieten CoolMOS Transistoren verglichen mit den schnellsten derzeit verfügbaren IGBTs nicht nur eine überlegene Stromtragfähigkeit (d.h. kleineste erforderliche Chipfläche bei gegebenem Strom, sondern auch den Vorteil einer intrinsischen Inversdiode. Besteht in einer Schaltung die Gefahr von parasitären Oszillationen mit ins Negative gehender Drain-Source-Spannung, so werden diese Unterschwinger durch die definierte Inversdiode geklemmt.

Ein für die Schaltungs-Auslegung interessanter Aspekt ergibt sich aus der neuen Abhängigkeit des  $R_{DS(on)}$  von der Sperrspannung: Bei allen Wandlertypen gilt, daß sich die übertragbare Leistung proportional zum Schalterstrom I und der Betriebsspannung  $U_{sw.eff}$  erhöht.

$$P_{OUT} \propto U \cdot I_{sw, eff} \tag{3.14}$$

Mit der Betriebsspannung steigt aber auch die erforderliche Sperrspannung des Schalters, und damit  $R_{DS(on)}$  bei gleichbleibender Chipfläche gemäß:

$$R_{DS(on)} \propto (U_{Br})^n$$

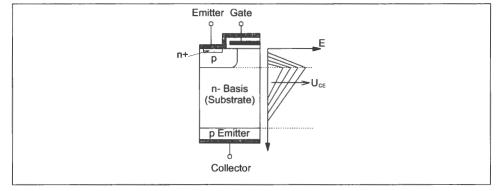

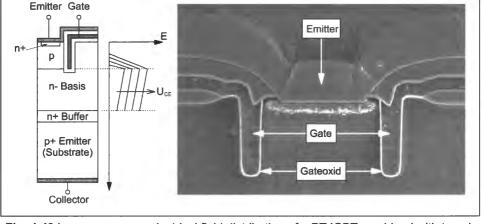

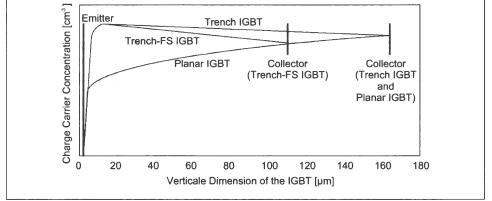

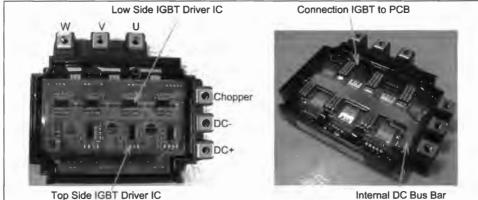

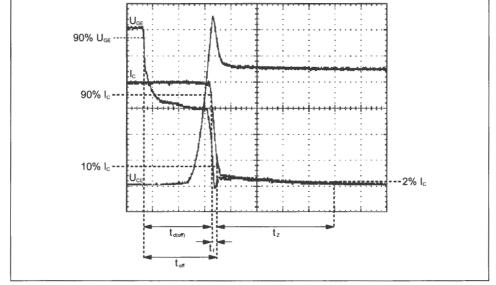

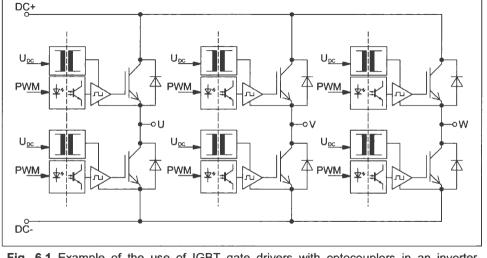

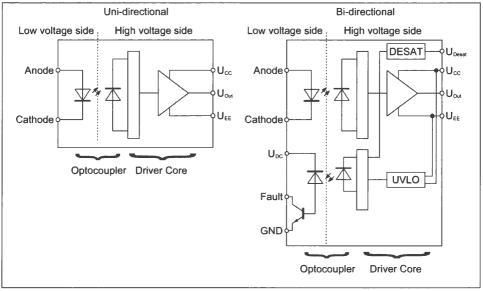

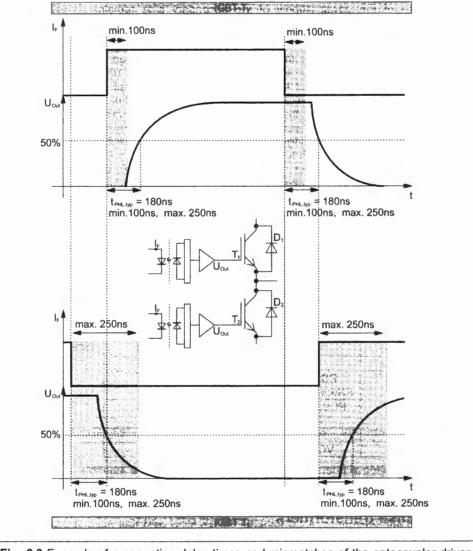

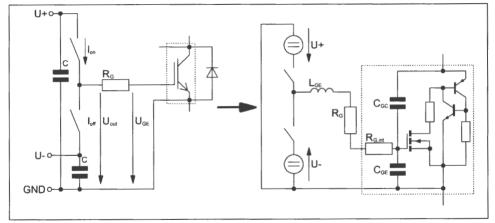

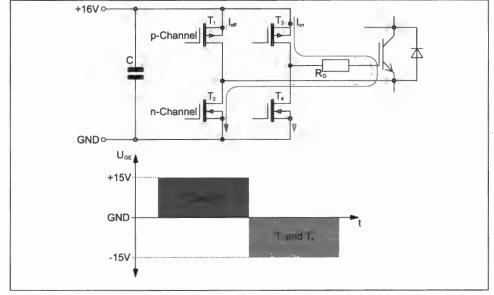

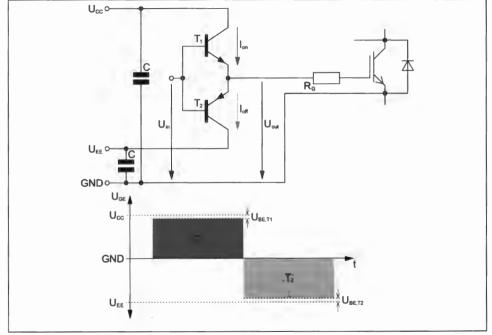

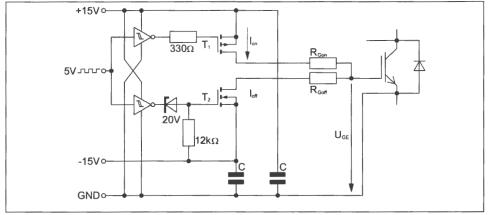

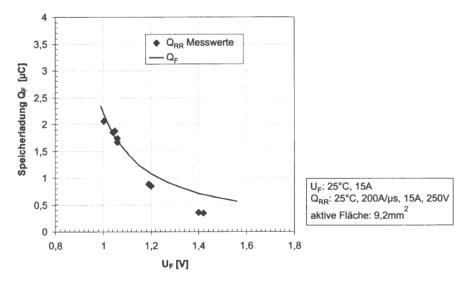

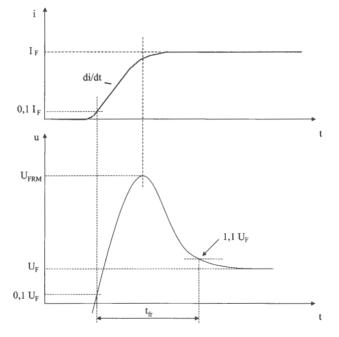

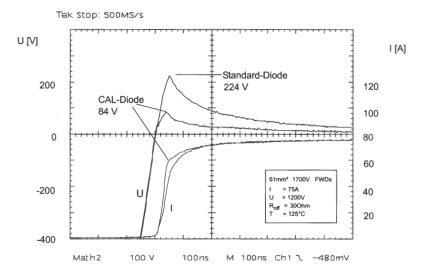

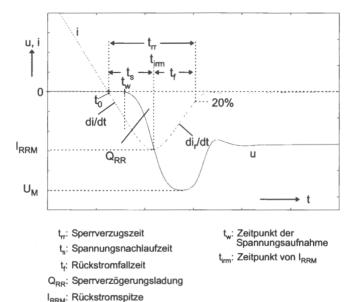

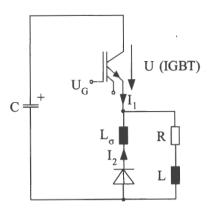

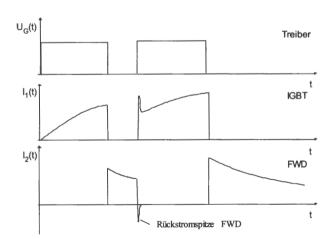

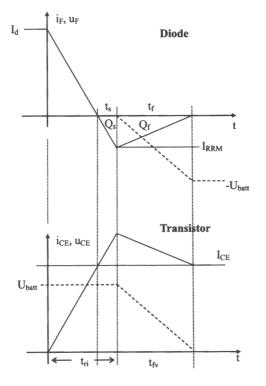

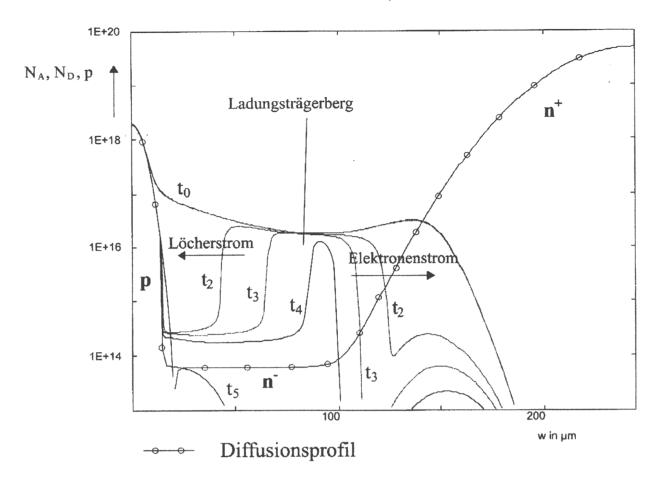

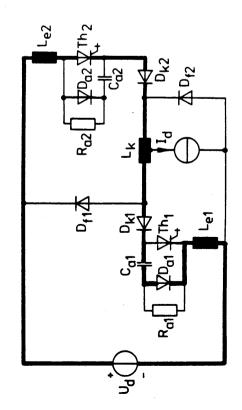

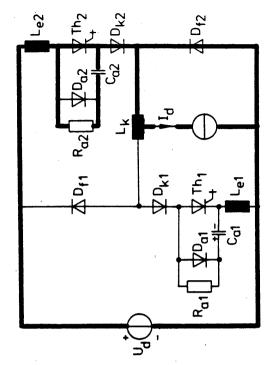

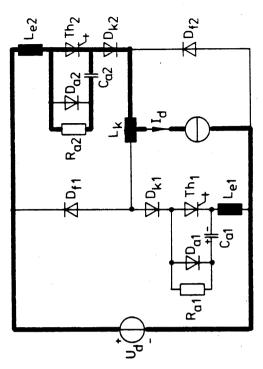

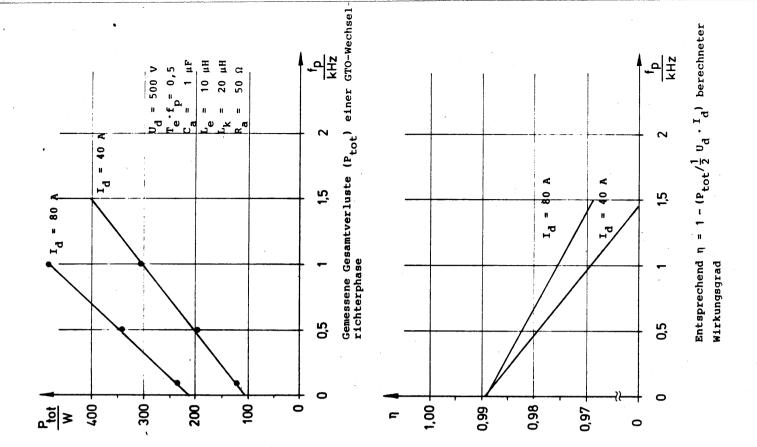

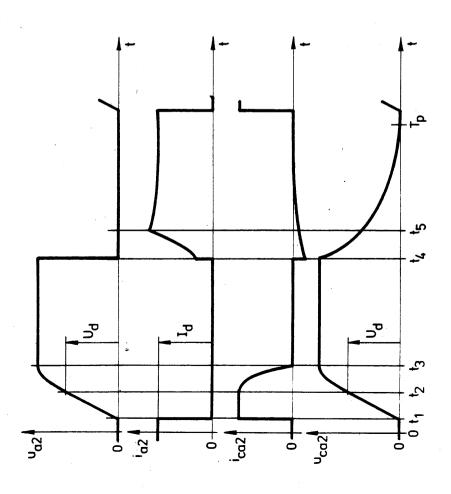

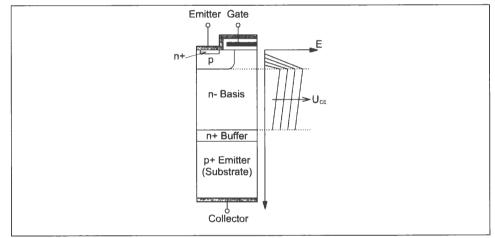

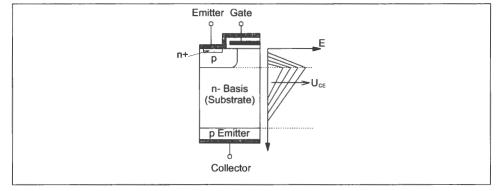

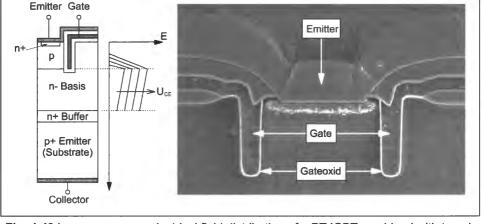

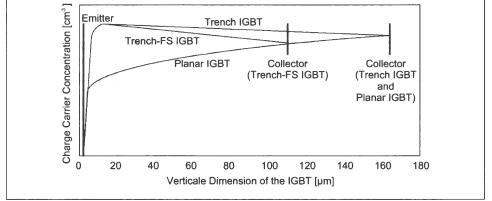

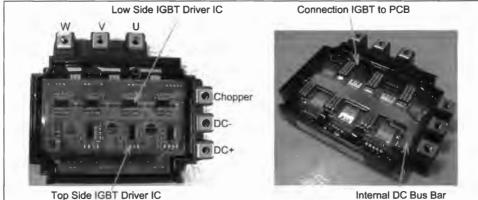

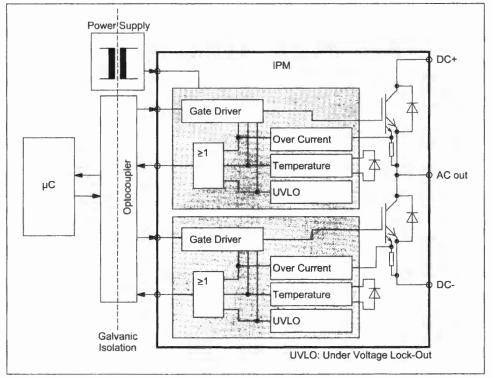

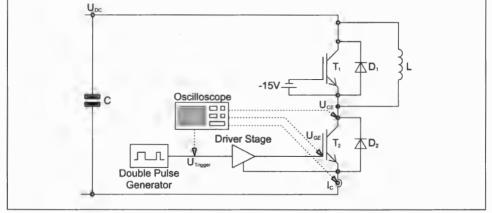

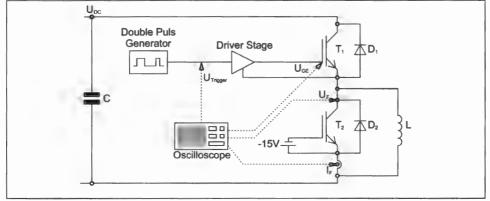

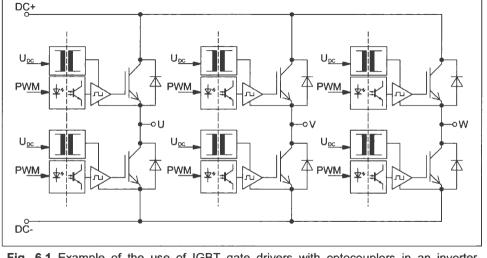

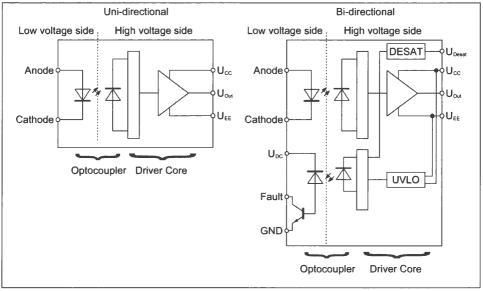

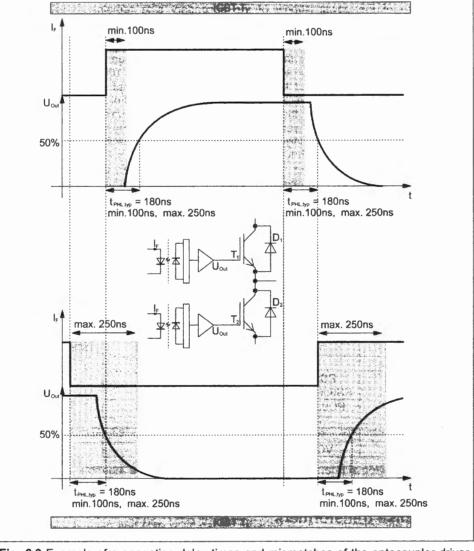

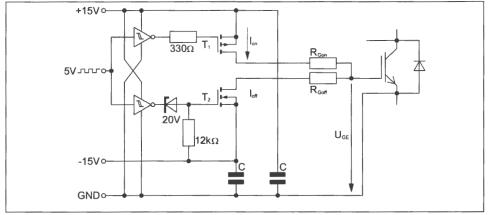

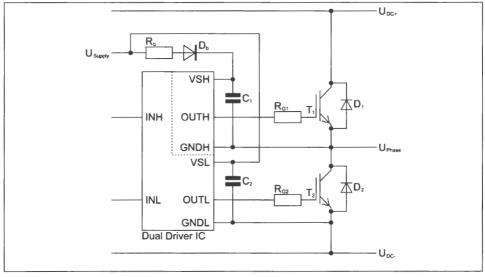

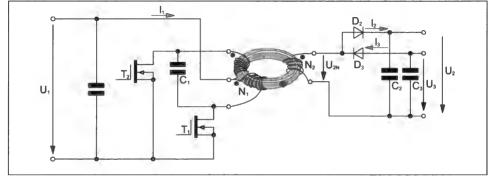

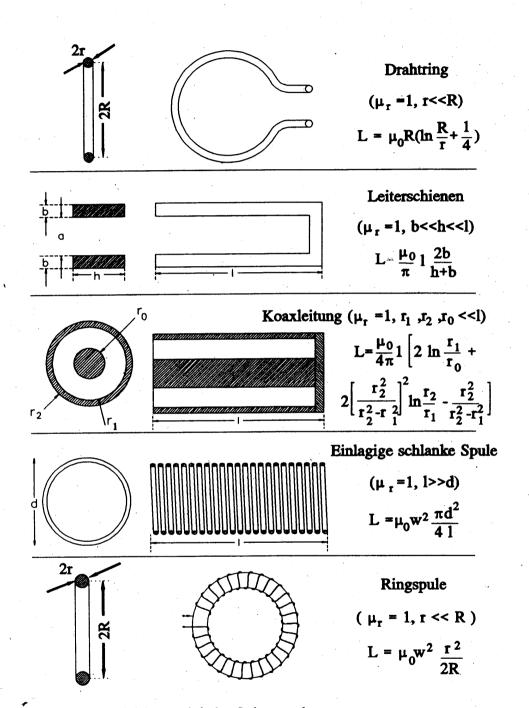

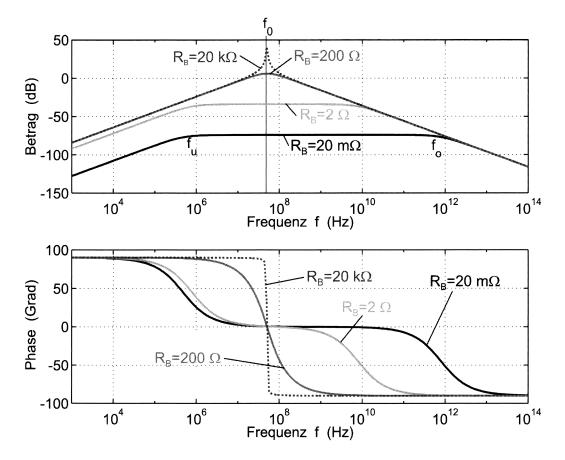

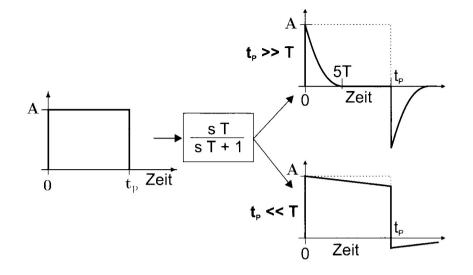

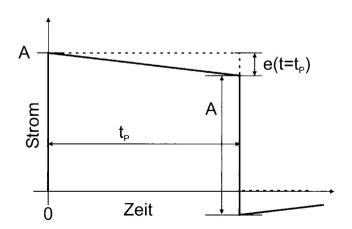

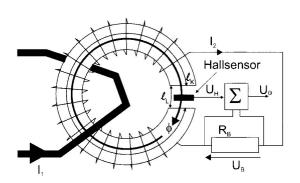

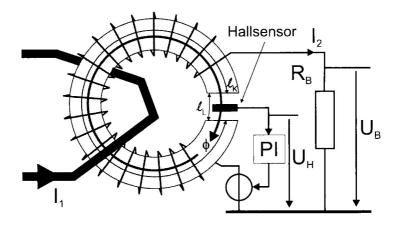

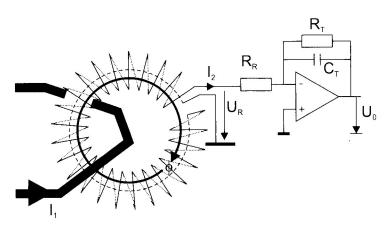

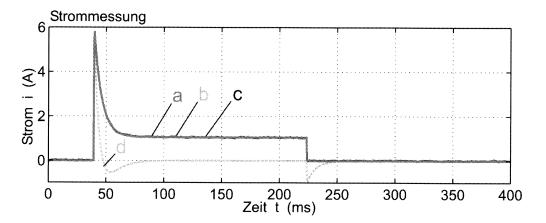

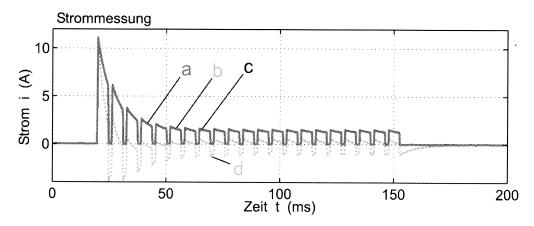

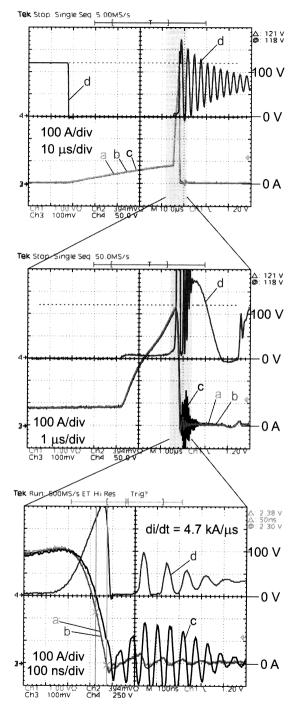

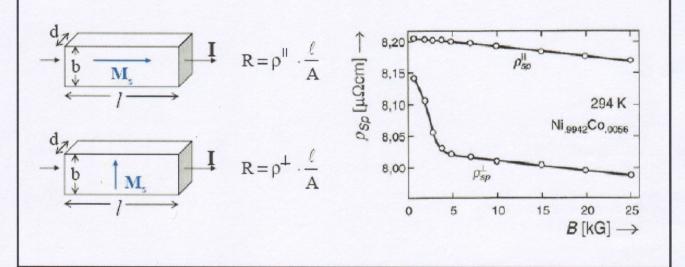

$n = \begin{cases} \frac{2.4 \text{ bis } 2.6}{1} \end{cases}$  Standard-MOS /CoolMOS (3.15)